# System Management Wizard v1.3

# LogiCORE IP Product Guide

**Vivado Design Suite**

PG185 April 6, 2016

# **Table of Contents**

#### **IP Facts**

| Chapter 1: Overview                 |   |

|-------------------------------------|---|

| Applications                        | 5 |

| Licensing and Ordering Information  | 7 |

| Chapter 2: Product Specification    |   |

| SYSMON Functional Features          | 3 |

| Standards                           | ) |

| Performance                         | 9 |

| Resource Utilization                | Э |

| Port Descriptions                   | Ð |

| Register Space 1                    | 3 |

| Chapter 3: Designing with the Core  |   |

| Clocking4                           | 5 |

| Resets                              | 5 |

| Protocol Description                | 7 |

| I2C Interface for SSIT Devices 4    | 7 |

| Chapter 4: Design Flow Steps        |   |

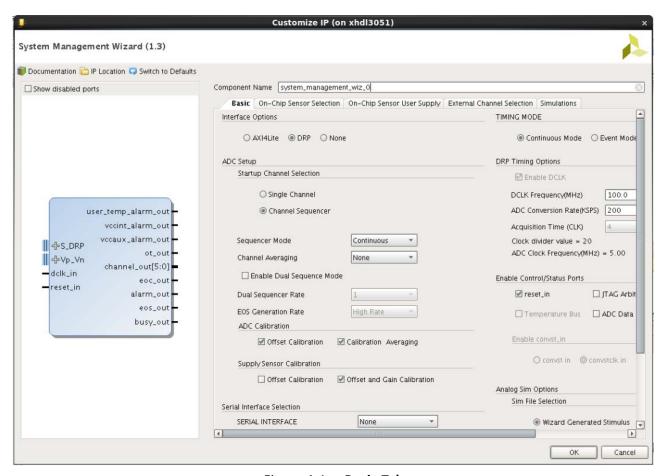

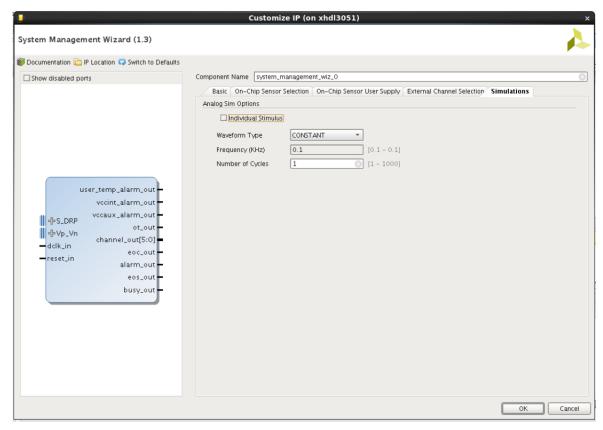

| Customizing and Generating the Core | ) |

| Constraining the Core               | Э |

| Simulation 70                       | ) |

| Synthesis and Implementation        | ) |

| Chapter 5: Example Design           |   |

| Open Example Project Flow 72        | 2 |

| Chapter 6: Test Bench               |   |

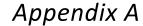

| Appendix A: Debugging               |   |

| Finding Help on Xilinx.com          | 1 |

| Debug Tools                         | ŝ |

| Simulation Debug                                       | <br>76 |

|--------------------------------------------------------|--------|

| Hardware Debug                                         | <br>78 |

| Interface Debug                                        | <br>78 |

| Anne and the Decade Additional Decade and Legal Mating |        |

| Appendix B: Additional Resources and Legal Notices     |        |

|                                                        |        |

| Xilinx Resources                                       | <br>79 |

| Xilinx Resources                                       |        |

|                                                        | <br>79 |

# Introduction

The LogiCORE™ IP System Management Wizard provides a complete solution for system-monitoring Xilinx UltraScale™ devices. This IP generates an HDL wrapper to configure the SYSMON for user-specified external channels, internal sensor channels, modes of operation and alarms. This IP supports monitoring of up to four user supplies. In addition, the System Management Wizard configures various interfaces for accessing SYSMON registers.

### **Features**

- On-chip voltage and temperature measurements

- 10-bit 0.2 MSPS analog-to-digital conversion

- Access to 16 pairs of I/O pins as input channels

- Stand-alone measurement of system functionality including sequences and alarms

- Triple access (FPGA Fabric/JTAG/I2C) DRP including control and status registers

- Optional AXI4-Lite interface based on the AXI4 specification

- Optional I<sup>2</sup>C interface

- Easy configuration of various modes and parameters

- Simple interface for channel selection and configuration

- Ability to select/deselect alarm outputs and set alarm limits

- Calculates all attributes of the Primitive based on user requirements

| LogiCORE IP Facts Table                   |                                                                             |  |  |  |  |

|-------------------------------------------|-----------------------------------------------------------------------------|--|--|--|--|

|                                           | Core Specifics                                                              |  |  |  |  |

| Supported<br>Device Family <sup>(1)</sup> | UltraScale™, UltraScale+                                                    |  |  |  |  |

| Supported User<br>Interfaces              | AXI4-Lite, DRP, I2C, PMBus <sup>(2)</sup>                                   |  |  |  |  |

| Resources                                 | Performance and Resource Utilization web page                               |  |  |  |  |

|                                           | Provided with Core                                                          |  |  |  |  |

| Design Files                              | Verilog and VHDL                                                            |  |  |  |  |

| Example Design                            | Verilog                                                                     |  |  |  |  |

| Test Bench                                | Verilog                                                                     |  |  |  |  |

| Constraints File                          | XDC                                                                         |  |  |  |  |

| Simulation<br>Model                       | Not Provided                                                                |  |  |  |  |

| Supported<br>S/W Driver                   | Standalone                                                                  |  |  |  |  |

|                                           | Tested Design Flows <sup>(3)</sup>                                          |  |  |  |  |

| Design Entry                              | Vivado® Design Suite                                                        |  |  |  |  |

| Simulation                                | For supported simulators, see the Xilinx Design Tools: Release Notes Guide. |  |  |  |  |

| Synthesis                                 | Vivado Synthesis                                                            |  |  |  |  |

|                                           | Support                                                                     |  |  |  |  |

| Provided b                                | Provided by Xilinx at the Xilinx Support web page                           |  |  |  |  |

#### Notes:

- 1. For a complete list of supported devices, see the Vivado IP catalog .

- 2. PMBus is supported for UltraScale+ only.

- 3. For the supported versions of the tools, see the Xilinx Design Tools: Release Notes Guide.

# Overview

The System Management Wizard guides you through configuring the SYSMON primitive through a user-friendly GUI and generates Verilog and VHDL Register Transfer Level (RTL) source files for Xilinx® UltraScale™ and UltraScale+ FPGAs.

**IMPORTANT:** Throughout this Product Guide, references to SYSMON point to SYSMONE1 in UltraScale and SYSMONE4 in UltraScale+ devices.

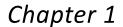

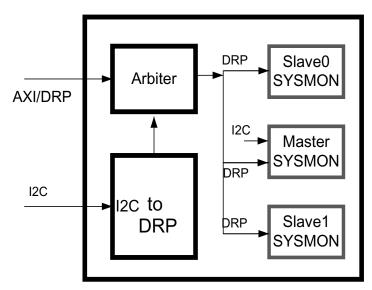

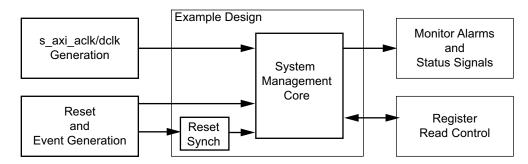

The System Management Wizard does not have access to the PS SYSMON in UltraScale+devices. It instantiates PL SYSMONE4 and adds new features. An example design and simulation test bench demonstrate how to integrate the core into user designs. The top-level block diagram for the System Management Wizard is shown in Figure 1-1.

Figure 1-1: System Management Wizard Block Diagram

# **Applications**

The System Management Wizard enables you to configure the integrated system management functions of the FPGA, such as monitoring user supplies and temperature.

# **Licensing and Ordering Information**

### **License Checkers**

If the IP requires a license key, the key must be verified. The Vivado® design tools have several license checkpoints for gating licensed IP through the flow. If the license check succeeds, the IP can continue generation. Otherwise, generation halts with error. License checkpoints are enforced by the following tools:

- Vivado design tools: Vivado Synthesis

- Vivado Implementation

- write\_bitstream (Tcl command)

**IMPORTANT:** IP license level is ignored at checkpoints. The test confirms a valid license exists. It does not check IP license level.

### **License Type**

This Xilinx LogiCORE™ IP module is provided at no additional cost with the Xilinx Vivado Design Suite under the terms of the Xilinx End User License. Information about this and other Xilinx LogiCORE IP modules is available at the Xilinx Intellectual Property page. For information about pricing and availability of other Xilinx LogiCORE IP modules and tools, contact your local Xilinx sales representative.

# **Product Specification**

The System Management Wizard instantiates a SYSMON block for UltraScale configured to your requirements. The wizard allows you to select the channels, enable alarms, and set the alarm limits. For interfaces, you can select AXI4-Lite, DRP, or None. In addition to these interfaces, the wizard also supports I<sup>2</sup>C and PMBus serial interfaces.

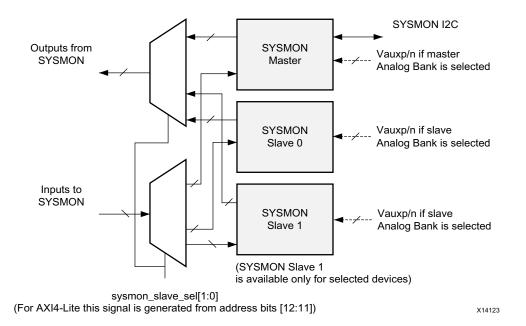

Stacked Silicon Interconnect (SSI) Kintex® UltraScale™ devices (XCKU100 and XCKU115) contain two SYSMON blocks, and Virtex® UltraScale devices (XCVU125, XCVU160, XCVU190 and XCVU440) and all Ultrascale + contain up to three SYSMON blocks. Each die in SSI device contains a SYSMON block in it.

## SYSMON Functional Features

Major functional SYSMON features common to SYSMONE1 and SYSMONE4 can be used to determine an appropriate mode of operation. These features include:

- FPGA temperature and voltage monitoring

- · Analog-to-digital conversion for seventeen external analog inputs

- Alarm generation based on up to 17 set parameters

#### **Additional Features of SYSMONE4**

- Direct access to measured data through ADC\_DATA port

- Monitoring of PS supplies (VCCPSINTLP, VCCPSINTFP, VCCPSAUX)

- Additional system monitor within PS can operate up to 1 MSPS

- Dual sequence

- SMBALERT for power management bus (PMBus) applications

- Common-N reduces package pins for auxiliary analog inputs by sharing a single N for single ended

# **Standards**

The System Management Wizard core contains AXI4-Lite interfaces, which is based on the AMBA® AXI4 specification.

### **Performance**

If you enable averaging of the channel, data capture rate is reduced depending on the averaging selected. Choose the appropriate value to match your requirement. Analog input noise from the supply or board can alter the expected 10-bit digital output.

# **Maximum Frequencies**

The maximum s\_axi\_aclk/dclk clock frequency supported is 250 MHz.

Note: In SSIT devices, using the AXI Interface does not guarantee a frequency of 250 MHz.

### **Resource Utilization**

For details about resource utilization, visit Performance and Resource Utilization.

When only the DRP interface is selected, the System Management Wizard uses SYSMON primitive only. Therefore, no LUTs are used as resource.

The maximum clock frequency results are post-implementation using the default tool settings. The resource usage results do not include the characterization registers and represent the true logic used by the core. LUT counts include SRL16s or SRL32s.

Clock frequency does not take clock jitter into account and should be derated by an amount appropriate to the clock source jitter specification. The maximum achievable clock frequency and the resource counts might also be affected by other tool options, additional logic in the FPGA, different versions of Xilinx tools, and other factors.

# **Port Descriptions**

Table 2-1 lists the input and output ports provided from the System Management Wizard. Availability of ports is controlled by user-selected parameters. For example, when Dynamic Reconfiguration is selected, only ports associated with Dynamic Reconfiguration are

exposed. Any port that is not exposed is tied off or connected to a signal labeled as unused in the delivered source code.

Table 2-1: System Management Wizard I/O Signals

| Port                           | Direction | Description                                                                                                                                                                                                                                                                                          |  |

|--------------------------------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| di_in[15:0] <sup>(2)</sup>     | Input     | Input data bus for the dynamic reconfiguration port (DRP).                                                                                                                                                                                                                                           |  |

| sysmon_slave_sel[1:0]          | Input     | Selects master or slave SYSMON to access the DRP and control signals when <b>Interface Selection</b> is DRP. This port is only available for SSI devices.  • 00: Master SYSMON  • 01: Slave 0 SYSMON  • 10: Slave 1 SYSMON                                                                           |  |

| do_out[15:0]                   | Output    | Output data bus for the dynamic reconfiguration port.                                                                                                                                                                                                                                                |  |

| daddr_in[7:0]                  | Input     | Address bus for the dynamic reconfiguration port.                                                                                                                                                                                                                                                    |  |

| den_in                         | Input     | Enable signal for the dynamic reconfiguration port.                                                                                                                                                                                                                                                  |  |

| dwe_in                         | Input     | Write enable for the dynamic reconfiguration port.                                                                                                                                                                                                                                                   |  |

| dclk_in                        | Input     | Clock input for the dynamic reconfiguration port.                                                                                                                                                                                                                                                    |  |

| drdy_out                       | Output    | Data ready signal for the dynamic reconfiguration port.                                                                                                                                                                                                                                              |  |

| reset_in <sup>(2)</sup>        | Input     | Reset signal for the SYSMON control logic and maximum/ minimum registers.                                                                                                                                                                                                                            |  |

| convst_in                      | Input     | Convert start input. This input is used to control the sampling instant on the ADC input and is only used in Event Mode Timing (see <i>UltraScale Architecture System Monitor Advanced Specification User Guide</i> (UG580) [Ref 1]).                                                                |  |

| convstclk_in                   | Input     | Convert start input. This input is connected to a global clock input on the interconnect. Like CONVST, this input is used to control the sampling instant on the ADC inputs and is only used in Event Mode Timing. The frequency of this clock should be greater than or equal to the sampling rate. |  |

| vp_in vn_in                    | Input     | One dedicated analog-input pair. The SYSMON has one pair of dedicated analog-input pins that provide a differential analog input.                                                                                                                                                                    |  |

| vauxp15[15:0]<br>vauxn15[15:0] | Inputs    | 16 auxiliary analog-input pairs. Also, the SYSMON uses 16 differential digital-input pairs as low-bandwidth differential analog inputs. These inputs are configured as analog during FPGA configuration.                                                                                             |  |

| user_temp_alarm_out            | Output    | SYSMON temperature-sensor alarm output.                                                                                                                                                                                                                                                              |  |

| vccint_alarm_out               | Output    | SYSMON VCCINT-sensor alarm output.                                                                                                                                                                                                                                                                   |  |

| vccaux_alarm_out               | Output    | SYSMON VCCAUX-sensor alarm output.                                                                                                                                                                                                                                                                   |  |

| ot_out                         | Output    | Over-Temperature alarm output.                                                                                                                                                                                                                                                                       |  |

| channel_out[5:0]               | Outputs   | Channel selection outputs. The ADC input MUX channel selection for the current ADC conversion is placed on these outputs at the end of an ADC conversion.                                                                                                                                            |  |

Table 2-1: System Management Wizard I/O Signals (Cont'd)

| Port                            | Direction | Description                                                                                                                                                                                                                                                                                            |  |

|---------------------------------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| eoc_out                         | Output    | End of Conversion signal. This signal transitions to an active-High at the end of an ADC conversion when the measurement result is written to the status registers. For detailed information, see UltraScale Architecture System Monitor Advanced Specification User Guide (UG580) [Ref 1].            |  |

| eos_out                         | Output    | End of Sequence. This signal transitions to an active-High when the measurement data from the last channel in the Channel Sequencer is written to the status registers. For detailed information, see <i>UltraScale Architecture System Monitor Advanced Specification User Guide</i> (UG580) [Ref 1]. |  |

| busy_out                        | Output    | ADC busy signal. This signal transitions High during an ADC conversion. This signal transitions High for an extended period during calibration.                                                                                                                                                        |  |

| i2c_sclk                        | INOUT     | I <sup>2</sup> C clock signal.                                                                                                                                                                                                                                                                         |  |

| i2c_sda                         | INOUT     | I <sup>2</sup> C serial data signal.                                                                                                                                                                                                                                                                   |  |

| jtaglocked_out <sup>(2)</sup>   | Output    | Used to indicate that drp port has been locked by the JTAG or ${\rm I}^2{\rm C}$ interface.                                                                                                                                                                                                            |  |

| jtagmodified_out <sup>(2)</sup> | Output    | Used to indicate that a JTAG or I <sup>2</sup> C write to the drp has occurred.                                                                                                                                                                                                                        |  |

| jtagbusy_out <sup>(2)</sup>     | Output    | Used to indicate that a JTAG or I <sup>2</sup> C drp transaction is in progress.                                                                                                                                                                                                                       |  |

| vbram_alarm_out                 | Output    | SYSMON VBRAM sensor alarm output.                                                                                                                                                                                                                                                                      |  |

| muxaddr_out[4:0]                | Output    | Use in external multiplexer mode to decode external MUX channel.                                                                                                                                                                                                                                       |  |

| alarm_out                       | Output    | Logic OR of alarms. Can be used to flag occurrence of any alarm.                                                                                                                                                                                                                                       |  |

| s_axi_aclk                      | Input     | AXI Clock.                                                                                                                                                                                                                                                                                             |  |

| s_axi_aresetn <sup>(2)</sup>    | Input     | AXI Reset, Active-Low                                                                                                                                                                                                                                                                                  |  |

| s_axi_awaddr[12:0]              | Input     | AXI Write address. The write address bus gives the address of the write transaction.                                                                                                                                                                                                                   |  |

| s_axi_awvalid                   | Input     | Write address valid. This signal indicates that a valid write address and control information are available.                                                                                                                                                                                           |  |

| s_axi_awready                   | Output    | Write address ready. This signal indicates that the slave is ready to accept an address and associated control signals.                                                                                                                                                                                |  |

| s_axi_wdata[31:0]               | Input     | Write data.                                                                                                                                                                                                                                                                                            |  |

| s_axi_wstb[3:0]                 | Input     | Write strobes. This signal indicates which byte lanes to update in memory.                                                                                                                                                                                                                             |  |

| s_axi_wvalid                    | Input     | Write valid. This signal indicates that valid write data and strobes are available.                                                                                                                                                                                                                    |  |

| s_axi_wready                    | Output    | Write ready. This signal indicates that the slave can accept the write data.                                                                                                                                                                                                                           |  |

Table 2-1: System Management Wizard I/O Signals (Cont'd)

| Port                         | Direction | Description                                                                                                                                                                                       |  |

|------------------------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| s_axi_bresp[1:0]             | Output    | Write response. This signal indicates the status of the write transaction:  • 00 = OKAY (normal response)  • 10 = SLVERR (error condition)  • 11 = DECERR (not issued by core)                    |  |

| s_axi_bvalid                 | Output    | Write response valid. This signal indicates that a valid write response is available.                                                                                                             |  |

| s_axi_bready                 | Input     | Response ready. This signal indicates that the master can accept the response information.                                                                                                        |  |

| s_axi_araddr[12:0]           | Input     | Read address. The read address bus gives the address of a read transaction.                                                                                                                       |  |

| s_axi_arvalid                | Input     | Read address valid. This signal indicates, when High, that the read address and control information is valid and remains stable until the address acknowledgement signal, s_axi_arready, is High. |  |

| s_axi_arready                | Output    | Read address ready. This signal indicates that the slave is ready to accept an address and associated control signals.                                                                            |  |

| s_axi_rdata[31:0]            | Output    | Read data.                                                                                                                                                                                        |  |

| s_axi_rresp[1:0]             | Output    | Read response. This signal indicates the status of the read transfer.  • 00 = OKAY (normal response)  • 10 = SLVERR (error condition)  • 11 = DECERR (not issued by core)                         |  |

| s_axi_rvalid                 | Output    | Read valid. This signal indicates that the required read data is available and the read transfer can complete.                                                                                    |  |

| s_axi_rready                 | Input     | Read ready. This signal indicates that the master can accept the read data and response information.                                                                                              |  |

| temp_out[9:0] <sup>(3)</sup> | Output    | 10-bit temperature output bus for MIG. This should be connected to temperature input port of MIG.                                                                                                 |  |

| ip2intc_irpt                 | Output    | Interrupt Control Signal. This signal indicates, when High, that one of the selected interrupt, mentioned in the Interrupt Enable Register, occurred.                                             |  |

| adc_data_master              | Output    | Direct data output of analog to digital converted value of Master SYSMON.(Available for Ultrascale plus devices)                                                                                  |  |

| adc_data_slave0              | Output    | Direct data output of analog to digital converted value of Slave0 SYSMON.(Available for Ultrascale plus devices)                                                                                  |  |

| adc_data_slave1              | Output    | Direct data output of analog to digital converted value of Slave1 SYSMON.(Available for Ultrascale plus devices)                                                                                  |  |

| SMBALERT                     | Output    | Optional PMBus alert. When Low indicates a system fault that must be cleared using PMBus commands. Connect to SMBALERT_TS.(Available for Ultrascale plus devices)                                 |  |

| vccpsintlp_alarm_out         | Output    | PS SYSMON VCCPSINTLP sensor alarm output. This port is available only for zynq Ultrascale plus devices                                                                                            |  |

Table 2-1: System Management Wizard I/O Signals (Cont'd)

| Port                 | Direction | Description                                                                                           |

|----------------------|-----------|-------------------------------------------------------------------------------------------------------|

| vccpsintfp_alarm_out | Output    | PS SYSMON VCCPSINTFP sensor alarm output This port is available only for zynq Ultrascale plus devices |

| vccpsaux_alarm_out   | Output    | PS SYSMON VCCPSAUX sensor alarm output This port is available only for zynq Ultrascale plus devices   |

#### **Notes:**

- 1. AXI4-Lite ports are available only with the AXI4-Lite interface.

- 2. DRP, JTAG, and reset\_in ports are not available when AXI4-Lite interface is selected.

- 3. The temp\_out port is available only when AXI4-Lite interface is enabled.

# **Register Space**

The SYSMON functionality is configured through control registers. For more details, see control and status register information in *UltraScale Architecture System Monitor Advanced Specification User Guide* (UG580) [Ref 1].

Table 2-2 lists the attributes associated with these control registers. Control registers can be initialized using HDL by attaching HDL attributes to the SYSMON primitive instance and configuring them according to the information provided in Table 2-2. The control registers can also be initialized through the AXI4-Lite or DRP interfaces at runtime. The System Management Wizard simplifies the initialization of these control registers in the HDL instantiation by automatically configuring them to implement the operating behavior you specify in the Vivado® Integrated Design Environment (IDE).

Table 2-2: SYSMON Attributes

| Attribute             | Name                        | Control Reg<br>Address | Description                                                                                                                                                                                                     |

|-----------------------|-----------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT_40               | Configuration<br>Register 0 | 40h                    |                                                                                                                                                                                                                 |

| INIT_41               | Configuration<br>Register 1 | 41h                    | SYSMON configuration registers. For detailed information, see <i>UltraScale Architecture System Monitor</i>                                                                                                     |

| INIT_42               | Configuration<br>Register 2 | 42h                    | Advanced Specification User Guide (UG580) [Ref 1].                                                                                                                                                              |

| INIT_43               | Configuration<br>Register 3 | 43h                    |                                                                                                                                                                                                                 |

| INIT_48 to<br>INIT_4F | Sequence<br>Registers       | 48h to 4Fh             | Sequence registers used to program the Channel Sequencer function in the SYSMON. For detailed information, see <i>UltraScale Architecture System Monitor Advanced Specification User Guide</i> (UG580) [Ref 1]. |

Table 2-2: SYSMON Attributes (Cont'd)

| Attribute             | Name                                 | Control Reg<br>Address | Description                                                                                                                                                                             |

|-----------------------|--------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INIT_50 to<br>INIT_6F | Alarm Limits<br>Registers            | 50h to 6Fh             | Alarm threshold registers for the SYSMON alarm function. For detailed information, see <i>UltraScale Architecture System Monitor Advanced Specification User Guide</i> (UG580) [Ref 1]. |

| SIM_MONITO<br>R_ FILE | Simulation<br>Analog Entry –<br>File |                        | This is the text file that contains the analog input stimulus. This is used for simulation.                                                                                             |

# System Management Wizard Register Descriptions for AXI4-Lite Interface

AXI4-Lite address mapping to Hard Macro Register Address:

|    |    |    | SE | EL | 1  | SYSMON Macro Register Address | Х | Х |  |

|----|----|----|----|----|----|-------------------------------|---|---|--|

| 15 | 14 | 13 | 12 | 11 | 10 | 9 2                           | 1 | 0 |  |

Bits Description:

0-1: Don't Care

2-9: SYSMON Macro Register Address

10: Always set to 1

11-12: Sysmon Slave Select Signal

00 ' Master SYSMON

01 'Slave 0 SYSMON

10 'Slave 1 SYSMON

Sysmon Slave Select signals decides to which SYSMON on the FPGA the AXI interface is communicating to.

Table 2-3 lists the System Management Wizard IP Core registers and corresponding addresses.

Table 2-3: IP Core Registers

|                                                  | T                                          |                      |                                                                                                                                                                                |  |  |  |  |  |  |

|--------------------------------------------------|--------------------------------------------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| Base Address +<br>Offset (hex)                   | Register Name                              | Access<br>Type       | Description                                                                                                                                                                    |  |  |  |  |  |  |

| System Management Wizard Local Register Grouping |                                            |                      |                                                                                                                                                                                |  |  |  |  |  |  |

| C_BASEADDR + 0x00                                | Software Reset Register (SRR)              | W <sup>(1)</sup>     | Software Reset Register                                                                                                                                                        |  |  |  |  |  |  |

| C_BASEADDR + 0x04                                | Status Register (SR)                       | R <sup>(2)</sup>     | Status Register                                                                                                                                                                |  |  |  |  |  |  |

| C_BASEADDR + 0x08                                | Alarm Output Status<br>Register (AOSR)     | R <sup>(2)</sup>     | Alarm Output Status Register                                                                                                                                                   |  |  |  |  |  |  |

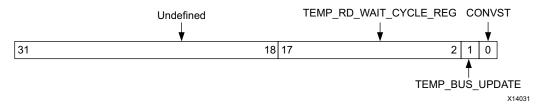

| C_BASEADDR + 0x0C                                | CONVST Register<br>(CONVSTR)               | W <sup>(1)</sup>     | <ul> <li>Bit[0] = ADC convert start register<sup>(3)</sup></li> <li>Bit[1] = Enable temperature update logic</li> <li>Bit[17:2] = Wait cycle for temperature update</li> </ul> |  |  |  |  |  |  |

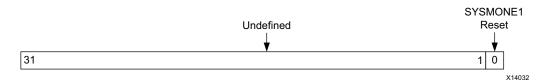

| C_BASEADDR + 0x10                                | SYSMON Reset Register (SYSMONRR)           | W <sup>(1)</sup>     | SYSMON Hard Macro Reset Register                                                                                                                                               |  |  |  |  |  |  |

| System Managemen                                 | t Wizard Interrupt Contro                  | oller Regist         | er Grouping                                                                                                                                                                    |  |  |  |  |  |  |

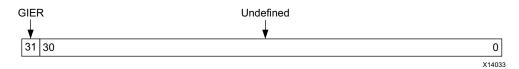

| C_BASEADDR + 0x5C                                | Global Interrupt Enable<br>Register (GIER) | R/W                  | Global Interrupt Enable Register                                                                                                                                               |  |  |  |  |  |  |

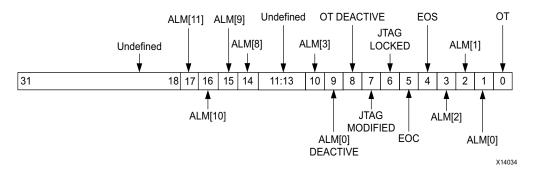

| C_BASEADDR + 0x60                                | IP Interrupt Status<br>Register (IPISR)    | R/TOW <sup>(4)</sup> | IP Interrupt Status Register                                                                                                                                                   |  |  |  |  |  |  |

| C_BASEADDR + 0x68                                | IP Interrupt Enable<br>Register (IPIER)    | R/W                  | IP Interrupt Enable Register                                                                                                                                                   |  |  |  |  |  |  |

| System Management                                | Wizard Hard Macro Reg                      | ister Group          | ing <sup>(5)</sup>                                                                                                                                                             |  |  |  |  |  |  |

| C_BASEADDR +<br>0x400                            | Temperature                                | R <sup>(6)</sup>     | 10-bit Most Significant Bit (MSB) justified result of on-device temperature measurement is stored in this register.                                                            |  |  |  |  |  |  |

| C_BASEADDR +<br>0x404                            | VCCINT                                     | R <sup>(6)</sup>     | The 10-bit MSB justified result of on-device VCCINT supply monitor measurement is stored in this register.                                                                     |  |  |  |  |  |  |

| C_BASEADDR +<br>0x408                            | VCCAUX                                     | R <sup>(6)</sup>     | The 10-bit MSB justified result of on-device VCCAUX Data supply monitor measurement is stored in this register.                                                                |  |  |  |  |  |  |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex)     | Register Name      | Access<br>Type     | Description                                                                                                                                                                                                                                                          |

|------------------------------------|--------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_BASEADDR +<br>0x40C              | VP/VN              | R/W <sup>(7)</sup> | <ul> <li>When read: The 10-bit MSB justified result of A/D conversion on the dedicated analog input channel (Vp/Vn) is stored in this register.</li> <li>When written: Write to this register resets the SYSMON hard macro. No specific data is required.</li> </ul> |

| C_BASEADDR +<br>0x410              | VREFP              | R <sup>(6)</sup>   | The 10-bit MSB justified result of A/D conversion on the reference input VREFP is stored in this register.                                                                                                                                                           |

| C_BASEADDR +<br>0x414              | VREFN              | R <sup>(6)</sup>   | The 10-bit MSB justified result of A/D conversion on the reference input VREFN is stored in this register.                                                                                                                                                           |

| C_BASEADDR +<br>0x418              | VBRAM              | R <sup>(6)</sup>   | The 10-bit MSB justified result of A/D conversion on the reference input VBRAM is stored in this register.                                                                                                                                                           |

| C_BASEADDR +<br>0x41C              | Undefined          | N/A                | These locations are unused and contain invalid data.                                                                                                                                                                                                                 |

| C_BASEADDR +<br>0x420              | Supply Offset      | R <sup>(6)</sup>   | The calibration coefficient for the supply sensor offset is stored in this register.                                                                                                                                                                                 |

| C_BASEADDR +<br>0x424              | ADC Offset         | R <sup>(6)</sup>   | The calibration coefficient for the ADC offset calibration is stored in this register.                                                                                                                                                                               |

| C_BASEADDR +<br>0x428              | Gain Error         | R <sup>(6)</sup>   | The calibration coefficient for the gain error is stored in this register.                                                                                                                                                                                           |

| C_BASEADDR + 0x434 (10)            | VCC_PSINTLP        | R                  | The 10-bit MSB justified result of A/D conversion on the reference input VCC_PSINTLP of Master SYSMON is Stored in this register.                                                                                                                                    |

| C_BASEADDR + 0x438 (10)            | VCC_PSINFP         | R                  | The 10-bit MSB justified result of A/D conversion on the reference input VCC_PSINFP of Master SYSMON is stored in this register                                                                                                                                      |

| C_BASEADDR + 0x43C <sup>(10)</sup> | VCC_PSAUX          | R                  | The 10-bit MSB justified result of A/D conversion on the reference input VCC_PSAUX of Master SYSMON is stored in this register                                                                                                                                       |

| C_BASEADDR +<br>0x440              | Vauxp[0]/ Vauxn[0] | R <sup>(6)</sup>   | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 0 is stored in this register.                                                                                                                                                        |

| C_BASEADDR +<br>0x444              | Vauxp[1]/ Vauxn[1] | R <sup>(6)</sup>   | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 1 is stored in this register.                                                                                                                                                        |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex) | Register Name        | Access<br>Type   | Description                                                                                                    |

|--------------------------------|----------------------|------------------|----------------------------------------------------------------------------------------------------------------|

| C_BASEADDR +<br>0x448          | VAUXP[2]/ VAUXN[2]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 2 is stored in this register.  |

| C_BASEADDR +<br>0x44C          | VAUXP[3]/ VAUXN[3]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 3 is stored in this register.  |

| C_BASEADDR +<br>0x450          | VAUXP[4]/ VAUXN[4]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 4 is stored in this register.  |

| C_BASEADDR +<br>0x454          | VAUXP[5]/ VAUXN[5]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 5 is stored in this register.  |

| C_BASEADDR +<br>0x458          | VAUXP[6]/ VAUXN[6]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 6 is stored in this register.  |

| C_BASEADDR +<br>0x45C          | VAUXP[7]/ VAUXN[7]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 7 is stored in this register.  |

| C_BASEADDR +<br>0x460          | VAUXP[8]/ VAUXN[8]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 8 is stored in this register.  |

| C_BASEADDR +<br>0x464          | VAUXP[9]/ VAUXN[9]   | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 9 is stored in this register.  |

| C_BASEADDR +<br>0x468          | VAUXP[10]/ VAUXN[10] | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 10 is stored in this register. |

| C_BASEADDR +<br>0x46C          | VAUXP[11]/ VAUXN[11] | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 11 is stored in this register. |

| C_BASEADDR +<br>0x470          | VAUXP[12]/ VAUXN[12] | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 12 is stored in this register. |

| C_BASEADDR +<br>0x474          | VAUXP[13]/ VAUXN[13] | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 13 is stored in this register. |

| C_BASEADDR +<br>0x478          | VAUXP[14]/ VAUXN[14] | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 14 is stored in this register. |

| C_BASEADDR +<br>0x47C          | VAUXP[15]/ VAUXN[15] | R <sup>(6)</sup> | The 10-bit MSB justified result of A/D conversion on the auxiliary analog input 15 is stored in this register. |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex)        | Register Name   | Access<br>Type   | Description                                                                |

|---------------------------------------|-----------------|------------------|----------------------------------------------------------------------------|

| C_BASEADDR +<br>0x480                 | Max Temp        | R <sup>(6)</sup> | The 10-bit MSB justified maximum temperature measurement.                  |

| C_BASEADDR +<br>0x484                 | Max VCCINT      | R <sup>(6)</sup> | The 10-bit MSB justified maximum VCCINT measurement.                       |

| C_BASEADDR +<br>0x488                 | Max Vccaux      | R <sup>(6)</sup> | The 10-bit MSB justified maximum VCCAUX measurement.                       |

| C_BASEADDR +<br>0x48C                 | Max VBRAM       | R <sup>(6)</sup> | The 10-bit MSB justified maximum VBRAM measurement.                        |

| C_BASEADDR + 0x490                    | Min Temp        | R <sup>(6)</sup> | The 10-bit MSB justified minimum temperature measurement                   |

| C_BASEADDR +<br>0x494                 | Min VCCINT      | R <sup>(6)</sup> | The 10-bit MSB justified minimum VCCINT measurement                        |

| C_BASEADDR +<br>0x498                 | Min VCCAUX      | R <sup>(6)</sup> | The 10-bit MSB justified minimum Vccaux measurement.                       |

| C_BASEADDR +<br>0x49C                 | Min VBRAM       | R <sup>(6)</sup> | The 10-bit MSB justified minimum VBRAM measurement.                        |

| C_BASEADDR + 0x4A0 (10)               | Max VCC_PSINTLP | R                | The 10-bit MSB justified maximum VCC_PSINTLP of Master SYSMON measurement. |

| C_BASEADDR +<br>0x4A4 <sup>(10)</sup> | Max VCC_PSINFP  | R                | The 10-bit MSB justified maximum VCC_PSINFP of Master SYSMON measurement.  |

| C_BASEADDR + 0x4A8 (10)               | Max VCC_PSAUX   | R                | The 10-bit MSB justified maximum VCC_PSAUX of Master SYSMON measurement.   |

| C_BASEADDR + 0x4AC (10)               | Undefined       | N/A              | These locations are unused and contain Invalid data.                       |

| C_BASEADDR + 0x4B0 (10)               | Min VCC_PSINTLP | R                | The 10-bit MSB justified minimum VCC_PSINTLP of Master SYSMON measurement. |

| C_BASEADDR +<br>0x4B4 <sup>(10)</sup> | Min VCC_PSINFP  | R                | The 10-bit MSB justified minimum VCC_PSINFP of Master SYSMON measurement.  |

| C_BASEADDR + 0x4B8 (10)               | MIn VCC_PSAUX   | R                | The 10-bit MSB justified minimums VCC_PSAUX of Master SYSMON measurement.  |

| C_BASEADDR + 0x4E0                    | I2C Address     | R                | The $I^2C$ address captured by initial conversion on $V_p/V_n$ channel.    |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex) | Register Name                 | Access<br>Type     | Description                                                                                                                                                                                                                     |

|--------------------------------|-------------------------------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| C_BASEADDR +<br>0x4FC          | Flag Register                 | R <sup>(6)</sup>   | The 16-bit register gives general status information of ALARM, Over Temperature (OT), disable information of SYSMON and information about whether the SYSMON is using internal reference voltage or external reference voltage. |

| C_BASEADDR +<br>0x500          | Configuration Register 0      | R/W <sup>(8)</sup> | SYSMON Configuration Register 0.                                                                                                                                                                                                |

| C_BASEADDR +<br>0x504          | Configuration Register 1      | R/W                | SYSMON Configuration Register 1.                                                                                                                                                                                                |

| C_BASEADDR +<br>0x508          | Configuration Register 2      | R/W                | SYSMON Configuration Register 2.                                                                                                                                                                                                |

| C_BASEADDR +<br>0x50C          | Configuration Register 3      | R/W                | SYSMON Configuration Register 3.                                                                                                                                                                                                |

| C_BASEADDR +<br>0x510          | Test Register                 | N/A                | SYSMON Test Register (For factory test only).                                                                                                                                                                                   |

| C_BASEADDR +<br>0x514          | Analog Bus Register           | N/A                | Configuration register for the Analog Bus.                                                                                                                                                                                      |

| C_BASEADDR +<br>0x518          | Sequence Register 8           | R/W                | Sequencer channel selection (Vuser0-3).                                                                                                                                                                                         |

| C_BASEADDR +<br>0x51C          | Sequence Register 9           | R/W                | Sequencer average selection (Vuser0-3).                                                                                                                                                                                         |

| C_BASEADDR +<br>0x520          | Sequence Register 0           | R/W                | SYSMON Sequence Register 0 (ADC channel selection).                                                                                                                                                                             |

| C_BASEADDR +<br>0x524          | Sequence Register 1           | R/W                | SYSMON Sequence Register 1 (ADC channel selection).                                                                                                                                                                             |

| C_BASEADDR +<br>0x528          | Sequence Register 2           | R/W                | SYSMON Sequence Register 2 (ADC channel averaging enable).                                                                                                                                                                      |

| C_BASEADDR +<br>0x52C          | Sequence Register 3           | R/W                | SYSMON Sequence Register 3 (ADC channel averaging enable).                                                                                                                                                                      |

| C_BASEADDR +<br>0x530          | Sequence Register 4           | R/W                | SYSMON Sequence Register 4 (ADC channel analog-input mode).                                                                                                                                                                     |

| C_BASEADDR +<br>0x534          | Sequence Register 5           | R/W                | SYSMON Sequence Register 5 (ADC channel analog-input mode).                                                                                                                                                                     |

| C_BASEADDR +<br>0x538          | Sequence Register 6           | R/W                | SYSMON Sequence Register 6 (ADC channel acquisition time).                                                                                                                                                                      |

| C_BASEADDR +<br>0x53C          | Sequence Register 7           | R/W                | SYSMON Sequence Register 7 (ADC channel acquisition time).                                                                                                                                                                      |

| C_BASEADDR +<br>0x540          | Alarm Threshold<br>Register 0 | R/W                | The 10-bit MSB justified alarm threshold register 0 (Temperature Upper).                                                                                                                                                        |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex) | Register Name                  | Access<br>Type     | Description                                                                                                           |

|--------------------------------|--------------------------------|--------------------|-----------------------------------------------------------------------------------------------------------------------|

| C_BASEADDR +<br>0x544          | Alarm Threshold<br>Register 1  | R/W                | The 10-bit MSB justified alarm threshold register 1 (VCCINT Upper).                                                   |

| C_BASEADDR +<br>0x548          | Alarm Threshold<br>Register 2  | R/W                | The 10-bit MSB justified alarm threshold register 2 (VCCAUX Upper).                                                   |

| C_BASEADDR +<br>0x54C          | Alarm Threshold<br>Register 3  | R/W <sup>(9)</sup> | The 10-bit MSB justified alarm threshold register 3 (OT Upper).                                                       |

| C_BASEADDR +<br>0x550          | Alarm Threshold<br>Register 4  | R/W                | The 10-bit MSB justified alarm threshold register 4 (Temperature Lower).                                              |

| C_BASEADDR +<br>0x554          | Alarm Threshold<br>Register 5  | R/W                | The 10-bit MSB justified alarm threshold register 5 (VCCINT Lower).                                                   |

| C_BASEADDR +<br>0x558          | Alarm Threshold<br>Register 6  | R/W                | The 10-bit MSB justified alarm threshold register 6 (VCCAUX Lower).                                                   |

| C_BASEADDR +<br>0x55C          | Alarm Threshold<br>Register 7  | R/W                | The 10-bit MSB justified alarm threshold register 7 (OT Lower)                                                        |

| C_BASEADDR +<br>0x560          | Alarm Threshold<br>Register 8  | R/W                | The 10-bit MSB justified alarm threshold register 8 (V <sub>BRAM</sub> Upper)                                         |

| C_BASEADDR +<br>0x570          | Alarm Threshold<br>Register 12 | R/W                | The 10-bit MSB justified alarm threshold register 12 (V <sub>BRAM</sub> Lower)                                        |

| C_BASEADDR +<br>0x580          | Alarm Threshold<br>Register 16 | R/W                | The 10-bit MSB justified alarm threshold register 16 (V <sub>USERO</sub> Upper)                                       |

| C_BASEADDR +<br>0x584          | Alarm Threshold<br>Register 17 | R/W                | The 10-bit MSB justified alarm threshold register 17 (V <sub>USER1</sub> Upper)                                       |

| C_BASEADDR +<br>0x588          | Alarm Threshold<br>Register 18 | R/W                | The 10-bit MSB justified alarm threshold register 18 (V <sub>USER2</sub> Upper)                                       |

| C_BASEADDR +<br>0x58C          | Alarm Threshold<br>Register 19 | R/W                | The 10-bit MSB justified alarm threshold register 19 (V <sub>USER3</sub> Upper)                                       |

| C_BASEADDR +<br>0x5A0          | Alarm Threshold<br>Register 22 | R/W                | The 10-bit MSB justified alarm threshold register 14 (V <sub>USER0</sub> Lower).                                      |

| C_BASEADDR +<br>0x5A4          | Alarm Threshold<br>Register 23 | R/W                | The 10-bit MSB justified alarm threshold register 15 (V <sub>USER1</sub> Lower).                                      |

| C_BASEADDR +<br>0x5A8          | Alarm Threshold<br>Register 24 | R/W                | The 10-bit MSB justified alarm threshold register 16 (V <sub>USER2</sub> Lower).                                      |

| C_BASEADDR +<br>0x5AC          | Alarm Threshold<br>Register 25 | R/W                | The 10-bit MSB justified alarm threshold register 17 (V <sub>USER3</sub> Lower).                                      |

| C_BASEADDR +<br>0x600          | V <sub>USER0</sub>             | R                  | The 10-bit MSB justified result of the on-chip $V_{\rm USER0}$ supply monitor measurement is stored at this location. |

| C_BASEADDR +<br>0x604          | V <sub>USER1</sub>             | R                  | The 10-bit MSB justified result of the on-chip $V_{\rm USER1}$ supply monitor measurement is stored at this location. |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex) | Register Name          | Access<br>Type | Description                                                                                                           |

|--------------------------------|------------------------|----------------|-----------------------------------------------------------------------------------------------------------------------|

| C_BASEADDR +<br>0x608          | V <sub>USER2</sub>     | R              | The 10-bit MSB justified result of the on-chip $V_{\rm USER2}$ supply monitor measurement is stored at this location. |

| C_BASEADDR +<br>0x60C          | V <sub>USER3</sub>     | R              | The 10-bit MSB justified result of the on-chip $V_{\rm USER3}$ supply monitor measurement is stored at this location. |

| C_BASEADDR +<br>0x680          | Max V <sub>USER0</sub> | R              | Maximum V <sub>USERO</sub> measurement recorded since power-up or the last System Monitor reset.                      |

| C_BASEADDR +<br>0x684          | Max V <sub>USER1</sub> | R              | Maximum V <sub>USER1</sub> measurement recorded since power-up or the last System Monitor reset.                      |

| C_BASEADDR +<br>0x688          | Max V <sub>USER2</sub> | R              | Maximum V <sub>USER2</sub> measurement recorded since power-up or the last System Monitor reset.                      |

| C_BASEADDR +<br>0x68C          | Max V <sub>USER3</sub> | R              | Maximum V <sub>USER3</sub> measurement recorded since power-up or the last System Monitor reset.                      |

| C_BASEADDR +<br>0x6A0          | Min V <sub>USER0</sub> | R              | Minimum V <sub>USER0</sub> measurement recorded since power-up or the last System Monitor reset.                      |

| C_BASEADDR +<br>0x6A4          | Min V <sub>USER1</sub> | R              | Minimum V <sub>USER1</sub> measurement recorded since power-up or the last System Monitor reset.                      |

| C_BASEADDR +<br>0x6A8          | Min V <sub>USER2</sub> | R              | Minimum V <sub>USER2</sub> measurement recorded since power-up or the last System Monitor reset.                      |

Table 2-3: IP Core Registers (Cont'd)

| Base Address +<br>Offset (hex) | Register Name          | Access<br>Type | Description                                                                                      |

|--------------------------------|------------------------|----------------|--------------------------------------------------------------------------------------------------|

| C_BASEADDR +<br>0x6Ac          | Min V <sub>USER3</sub> | R              | Minimum V <sub>USER3</sub> measurement recorded since power-up or the last System Monitor reset. |

#### **Notes:**

- 1. Reading of this register returns an undefined value.

- 2. Writing into this register has no effect.

- 3. Used in event-driven sampling mode only.

- 4. TOW = Toggle On Write. Writing a 1 to a bit position within the register causes the corresponding bit position in the register to toggle.

- 5. These are 16-bit registers internal to SYSMON. These are mapped to the lower-half word boundary on 32-bit System Management Wizard IP core registers.

- 6. Writing to this SYSMON hard macro register is not allowed. The SYSMON hard macro data registers are 16 bits in width. The SYSMON hard macro specification guarantees the first 10 MSB bits accuracy; so only these bits are used for reference.

- 7. Writing to this register resets the SYSMON hard macro. No specific data pattern is required to reset the SYSMON hard macro.

- 8. Read the SYSMON User Guide, for setting the different bits available in configuration registers for UltraScale devices.

- 9. The OT upper register is a user-configurable register for the upper threshold level of temperature. If this register is left unconfigured, then the SYSMON considers 125°C as the upper threshold value for OT. While configuring this register, the last four bits must be set to 0011, that is, Alarm Threshold Register 3[3:0] = 0011. The upper 12 bits of this register are user configurable.

- 10. These registers are valid for Zynq UltraScale+ devices only.

# System Management Wizard Local Register Grouping for AXI4-Lite Interface

It is expected that the System Management Wizard IP core registers are accessed in their preferred-access mode only. If a write attempt is made to read-only registers, there is no affect on register contents. If the write-only registers are read, the result is undefined data. All internal registers of the core must be accessed in 32-bit format. If there is any other kind of access (half-word or byte access) for local 32-bit registers, the transaction is completed with errors for the corresponding transaction.

#### Software Reset Register (SRR)

The Software Reset register permits you to reset the System Management Wizard IP core including the SYSMON hard macro output ports (except JTAG-related outputs) independently of other IP cores in the systems. To activate a software reset, write 0x0000\_000A to the register. Any other access, read or write, has undefined results. The bit assignment in the Software Reset register is shown in Figure 2-2 and described in Table 2-4.

Figure 2-2: Software Reset Register

Table 2-4: Software Reset Register Description (C\_BASEADDR + 0x00)

| Bits | Name  | Reset<br>Value | Access<br>Type | Description                                                                                                                                                             |

|------|-------|----------------|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:0 | Reset | N/A            | W              | The only allowed operation on this register is a write of 0x0000_000A, which resets the System Management Wizard IP Core. The reset is active only for 16 clock cycles. |

#### Status Register (SR)

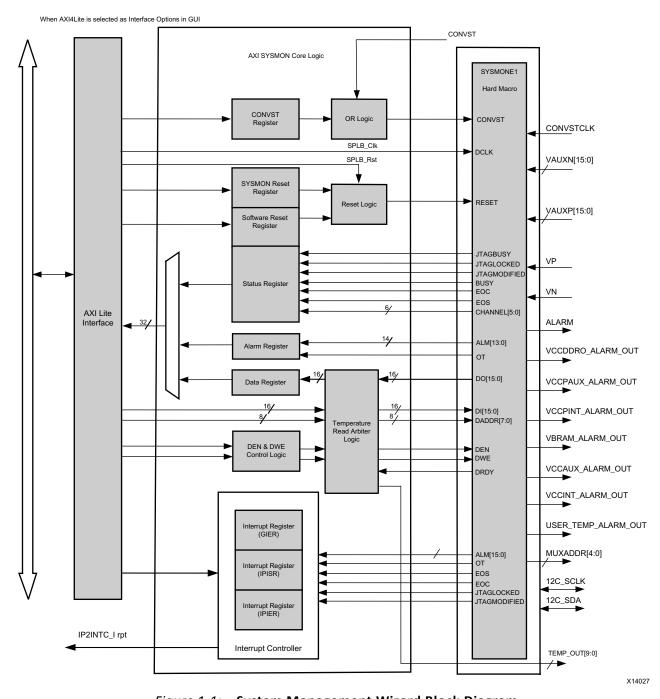

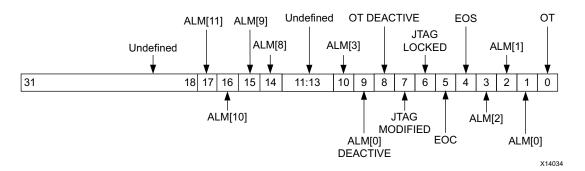

The Status register contains the System Management Wizard IP core channel status, EOC, EOS, and JTAG access signals. This register is read only. Any attempt to write the bits of the register is not able to change the bits. The Status Register bit definitions are shown in Figure 2-3 and explained in Table 2-5.

Figure 2-3: Status Register

Table 2-5: Status Register (C\_BASEADDR + 0x04)

| Bits  | Name             | Reset<br>Value | Access<br>Type | Description                                                                                                                                                                                                                                                            |

|-------|------------------|----------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:12 | Undefined        | N/A            | N/A            | Undefined                                                                                                                                                                                                                                                              |

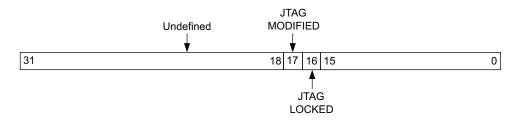

| 11    | JTAGBUSY         | 0              | R              | Used to indicate that a JTAG DRP or I <sup>2</sup> C transaction is in progress.                                                                                                                                                                                       |

| 10    | JTAG<br>MODIFIED | 0              | R              | Used to indicate that a write to DRP through JTAG interface or $I^2C$ transaction has occurred. This bit is cleared when a successful DRP read/write operation through the FPGA logic is performed. The DRP read/write through the FPGA logic fails, if JTAGLOCKED = 1 |

| 9     | JTAG<br>LOCKED   | 0              | R              | Used to indicate that a DRP port lock request has been made by the Joint Test Action Group (JTAG) interface.                                                                                                                                                           |

| 8     | BUSY             | N/A            | R              | ADC busy signal. This signal transitions High during an ADC conversion.                                                                                                                                                                                                |

|      |                  | _              |                |                                                                                                                                                                                                                                                          |

|------|------------------|----------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Bits | Name             | Reset<br>Value | Access<br>Type | Description                                                                                                                                                                                                                                              |

| 7    | EOS              | N/A            | R              | End of Sequence. This signal transitions to an active-High when<br>the measurement data from the last channel in the auto<br>sequence is written to the status registers. This bit is cleared<br>when a read operation is performed on status register.  |

| 6    | EOC              | N/A            | R              | End of Conversion signal. This signal transitions to an active-High at the end of an ADC conversion when the measurement is written to the SYSMON hard macro status register. This bit is cleared when a read operation is performed on status register. |

| 5:0  | CHANNEL<br>[5:0] | N/A            | R              | Channel selection outputs. The ADC input MUX channel selection for the current ADC conversion is placed on these outputs at the end of an ADC conversion.                                                                                                |

Table 2-5: Status Register (C\_BASEADDR + 0x04) (Cont'd)

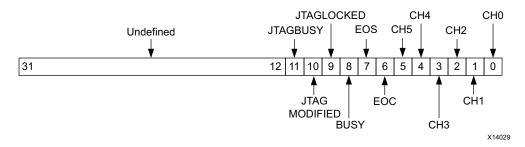

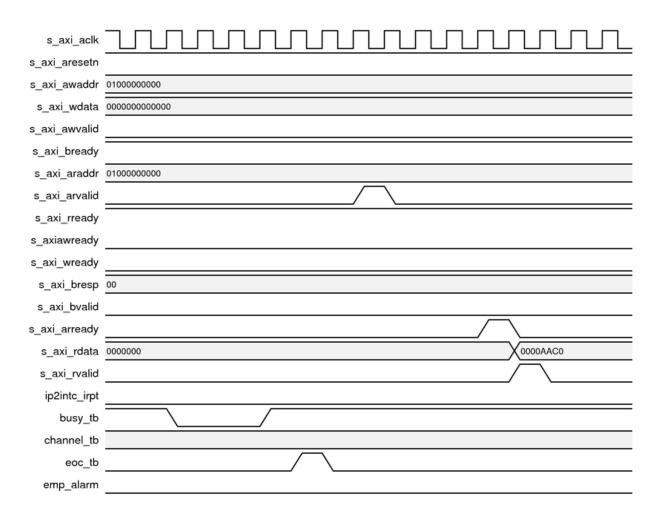

#### Alarm Output Status Register (AOSR)

The Alarm Output Status register contains all the alarm outputs for the System Management Wizard IP core. This register is read-only. Any attempt to write the bits of the register is not able to change the bits. The Alarm Output Status register bit definitions are shown in Figure 2-4 and explained in Table 2-6.

Figure 2-4: Alarm Output Status Register

Table 2-6: Alarm Output Status Register (C\_BASEADDR + 0x08)

| Bits  | Name      | Reset<br>Value | Access<br>Type | Description                                                                       |  |

|-------|-----------|----------------|----------------|-----------------------------------------------------------------------------------|--|

| 31:17 | Undefined | N/A            | N/A            | Undefined                                                                         |  |

| 16    | ALM[15]   | 0              | R              | Logical ORing of ALARM bits 8 to 14. This is direct output from the SYSMON macro. |  |

| 15:13 | Undefined | N/A            | N/A            | Reserved                                                                          |  |

| 12:9  | ALM[11:8] | 0              | R              | Alarms for User Supplies 0-3                                                      |  |

| 8     | ALM[7]    | 0              | R              | Logical ORing of ALARM bits 0 to 6. This is direct output from the SYSMON macro.  |  |

| Bits | Name     | Reset<br>Value | Access<br>Type | Description                                                                                                                                         |  |

|------|----------|----------------|----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 7:5  | ALM[6:4] | 0              | R              | Reserved                                                                                                                                            |  |

| 4    | ALM[3]   | 0              | R              | SYSMON VBRAM-Sensor Status. SYSMON VBRAM-sensor alarm output interrupt occurs when VBRAM exceeds user-defined threshold.                            |  |

| 3    | ALM[2]   | 0              | R              | SYSMON VCCAUX-Sensor Status. SYSMON VCCAUX-sensor alarm output interrupt occurs when VCCAUX exceeds user-defined threshold.                         |  |

| 2    | ALM[1]   | 0              | R              | SYSMON VCCINT-Sensor Status. SYSMON VCCINT-sensor alarm output interrupt occurs when VCCINT exceeds user-defined threshold.                         |  |

| 1    | ALM[0]   | 0              | R              | SYSMON Temperature-Sensor Status. SYSMON temperature-sensor alarm output interrupt occurs when device temperature exceeds user-defined threshold.   |  |

| 0    | ОТ       | 0              | R              | SYSMON Over-Temperature Alarm Status. Over-Temperature alarm output interrupt occurs when the die temperature exceeds a factory set limit of 125°C. |  |

Table 2-6: Alarm Output Status Register (C\_BASEADDR + 0x08) (Cont'd)

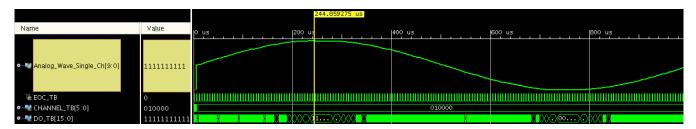

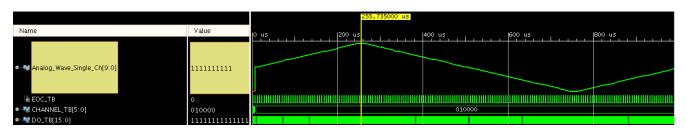

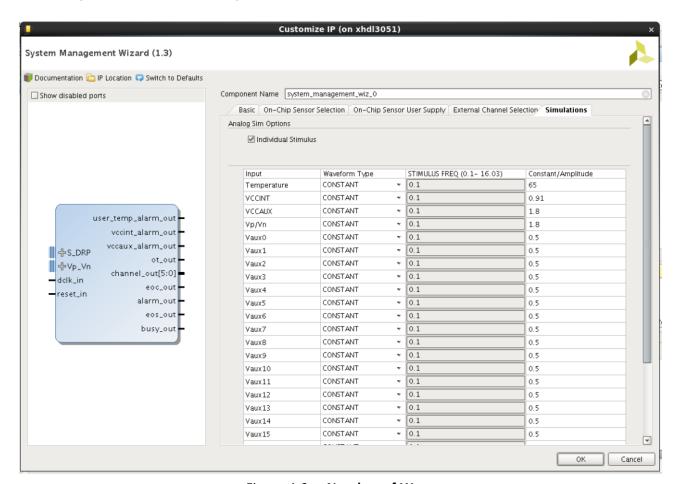

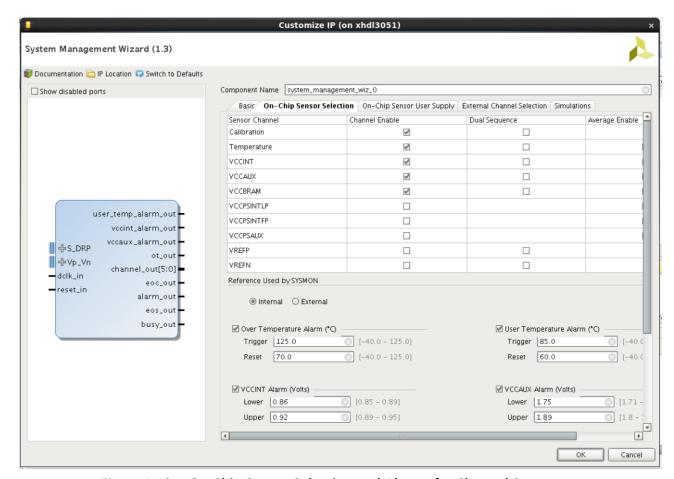

#### **CONVST Register (CONVSTR)**