# ADDENDUM MANUAL

# **MODEL 7807 – OPTION 110**

XMC PCI Express Carrier – Optical Interface Programming

Pentek, Inc. One Park Way Upper Saddle River, NJ 07458 (201) 818–5900 http://www.pentek.com

Copyright © 2015

Manual Part No: 800.78071

Rev: 0.1 – May 1, 2015

#### Manual Revision History

#### **Comments**

DateRevision5/1/150.1Initial release.

#### **Warranty**

Pentek warrants that all products manufactured by Pentek conform to published Pentek specifications and are free from defects in materials and workmanship for a period of one year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished. The obligation of Pentek arising from a warranty claim shall be limited to repairing or at its option, replacing without charge, any product that in Pentek's sole opinion proves to be defective within the scope of the warranty. Pentek must be notified in writing of the defect or nonconformity within the warranty period and the affected product returned to Pentek within thirty days after discovery of such defect or nonconformity. Buyer shall prepay shipping charges, taxes, duties and insurance for products returned to Pentek for warranty service. Pentek shall pay for the return of products to buyer except for products returned from another country.

Pentek shall have no responsibility for any defect or damage caused by improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, or accident, or for any product that has been repaired or altered by anyone other than Pentek or its authorized representatives.

The warranty described above is buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Pentek specifically disclaims fitness for a particular purpose. Under no circumstances shall Pentek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

#### Copyrights

With the exception of those items listed below, the contents of this publication are Copyright © 2015, Pentek, Inc. All Rights Reserved. Contents of this publication may not be reproduced in any form without written permission.

#### **Trademarks**

Onyx, Pentek, GateFlow, and ReadyFlow are registered trademarks or trademarks of Pentek, Inc.

FireFly is a trademark of Samtec, Inc.

# Table of Contents

## Page

## Chapter 1: Model 7807–110 Optical Programming

| 1.1 | Overvi  | ew                                               | 5   |

|-----|---------|--------------------------------------------------|-----|

| 1.2 | TWSI (  | (I2C) Bus Interface                              | 5   |

|     | Figure  | 1-1: TWSI Bus interfaces                         | 5   |

| 1.3 | 0       | Receive and Transmit Modules Programming         |     |

| 1.4 | 2       | 35 Programming                                   |     |

| 1.5 |         | i35 Port A – Optical Receive                     |     |

|     | 1.5.1   | Port A, Register 0 – Input Data (READ ONLY)      |     |

|     |         | Table 1–1: PCA Register 0: Port A Data Input     |     |

|     |         | 1.5.1.1 OPT_RX_INTL                              |     |

|     |         | 1.5.1.2 OPT_RX_PRESENTL                          | 7   |

|     | 1.5.2   | Port A, Register 2 – Output Data (WRITE ONLY)    | 8   |

|     |         | Table 1–2: PCA Register 2: Port A Data Output    |     |

|     |         | 1.5.2.1 OPT_RX_RESETL                            |     |

|     |         | 1.5.2.2 OPT_RX_SELECTL                           |     |

|     | 1.5.3   | Port A, Register 4 – Polarity Control            |     |

|     | 1.5.4   | Port A, Register 6 – I/O Control                 |     |

|     |         | Table 1–3: PCA Register 6: Port A I/O Control    |     |

| 1.6 | PCA95   | 35 Port B – Optical Transmit                     |     |

|     | 1.6.1   | Port B, Register 1 – Input Data (READ ONLY)      | 9   |

|     |         | Table 1–4: PCA Register 1: Port B Data Input     |     |

|     |         | 1.6.1.1 OPT_TX_INTL                              |     |

|     |         | 1.6.1.2 OPT_TX_PRESENTL                          |     |

|     | 1.6.2   | Port B, Register 3 – Output Data (WRITE ONLY)    |     |

|     |         | Table 1–5: PCA Register 3: Port B Data Output    |     |

|     |         | 1.6.2.1 OPT_TX_RESETL                            |     |

|     |         | 1.6.2.2 OPT_TX_SELECTL                           |     |

|     | 1.6.3   | Port B, Register 5 – Polarity Control            |     |

|     | 1.6.4   | Port B, Register 7 – I/O Control                 |     |

|     |         | Table 1–6: PCA Register 7: Port B I/O Control    | 10  |

|     |         | Appendix A: Phillips Semiconductors Corporation, |     |

|     |         | PCA9535 Data Sheet                               |     |

|     |         |                                                  |     |

| A.1 | Introdu | uction                                           | A–1 |

|     |         |                                                  |     |

## Appendix B: Samtec Inc, FireFly™ Optical User Manual

| B.1 | Introduction | B- | 1 |

|-----|--------------|----|---|

|-----|--------------|----|---|

Table of Contents

Page

This page is intentionally blank

# Chapter 1: Model 7807–110 Optical Programming

## 1.1 Overview

This addendum to the Model 7807 Operating Manual (800.78070) and the Onyx® Model 787xx series Installation Manuals (800.787xx) describes operation and programming of the Model 7807 Option 110 optical interface. Refer to the Model 7807 Operating Manual (800.78070) or the Onyx Model 787xx Installation Manual (800.787xx) provided with your shipment for description of the hardware and connections referenced in this addendum.

In addition to the programming instructions provided in this Option 110 Addendum Manual, copies of the manufacturers datasheets for the programmable devices in this optical interface are provided in the Appendices to this addendum manual.

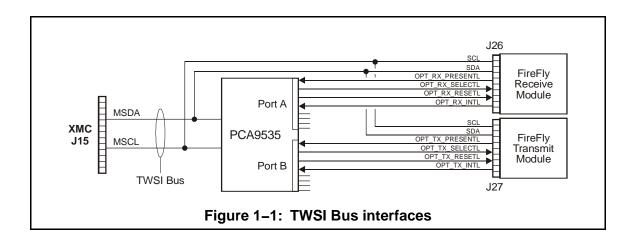

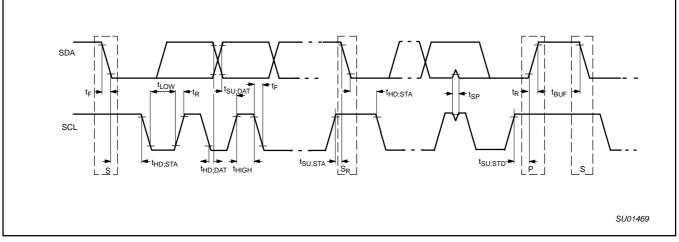

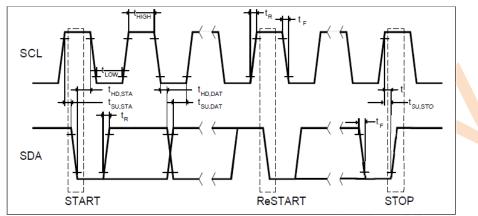

## 1.2 TWSI (I<sup>2</sup>C) Bus Interface

Programmable devices for the Option 110 optical interface are accessed using a TWSI (I<sup>2</sup>C) bus interface. This bus is a two–wire, serial data (SDA) and serial clock (SCL), bi–directional bus, derived from the **J15 MSDA** and **MSCL** signals from the XMC mounted on the 7807. Refer to the operating manual for the Pentek XMC module you are using (800.717xx for a Pentek Onyx Model 787xx) for information on accessing this TWSI bus from the XMC.

The TWSI bus provides programming signals to the Samtec FireFly<sup>™</sup> active optical receive and transmit modules connected to the 7807 connectors **J26** and **J27** (described in the Model 7807 Operating Manual, 800.78070). The TWSI bus provides access to a Philips Semiconductors PCA9535 I/O port serial to parallel converter for discrete control lines, and to the FireFly Receive and Transmit modules for device programming, as illustrated below.

## **1.2 TWSI (I<sup>2</sup>C) Bus Interface** (continued)

The devices on the TWSI bus are accessed at the following bus addresses.

| Device                  | Binary bus address | Description |

|-------------------------|--------------------|-------------|

| FireFly Receive module  | 1010100h           | Section 1.3 |

| FireFly Transmit module | 1010000h           | Section 1.3 |

| PCA9535                 | 0100000h           | Section 1.4 |

## **1.3** FireFly Receive and Transmit Modules Programming

The Samtec FireFly optical receive (**RX**) and transmit (**TX**) modules used with the 7807 each have a control interface on the TSWI bus at binary address 1010100h for receive module, and at binary address 1010000h for transmit module. Each module has a discrete select line that enables that module to send/receive data from the TWSI bus.

- Bit 1 of the PCA9535 Port A Register 2 (OPT\_RX\_SELECTL, Section 1.5.2.2) enables the optical receive module to send/receive data on the TWSI bus at binary address 1010100h

- Bit 1 of the PCA9535 Port B Register 3 (OPT\_TX\_SELECTL, Section 1.6.2.2) enables the optical transmit module to send/receive data on the TWSI bus at binary address 1010000h

Each FireFly module has internal registers that must be set up using the TWSI bus interface. Refer to the Samtec FireFly Optical User Manual, Appendix B, for programming information.

## 1.4 PCA9535 Programming

Model 7807 uses a Philips Semiconductors PCA9535 I<sup>2</sup>C I/O port device, which is at binary address 0100000h on the TWSI bus. The PCA9535 has two 8–bit I/O ports; each port I/O pin can be configured as either input or output. The PCA9535 has eight registers for programming the function of each pin, and reading from or writing to the pins.

The use of each I/O port is:

- Port A Optical Receive Control, Section 1.5 two input and two output pins

- Port B Optical Transmit Control, Section 1.6 two input and two output pins

Refer to the Philips Semiconductors Corporation PCA9535 Data Sheet, Appendix A, for programming information.

## 1.5 PCA9535 Port A – Optical Receive

PCA9535 Port A is connected to the optical receive module control connector **J26**, and is used to program the active interface and read status from it. Port A is accessed and controlled using PCA9535 internal registers 0, 2, 4, and 6 as follows:

- Register 0 Data input from Port A

- Register 2 Data output to Port A

- Register 4 Invert input data from Port A

- Register 6 I/O control of Port A

## 1.5.1 Port A, Register 0 – Input Data (READ ONLY)

|          | Table 1–1: PCA Register 0: Port A Data Input |                                   |                   |                                |  |  |

|----------|----------------------------------------------|-----------------------------------|-------------------|--------------------------------|--|--|

|          | 7 – 4                                        | 3                                 | 2 – 1             | 0                              |  |  |

| Bit Name | NOT USED                                     | OPT_RX_INTL                       | NOT USED          | OPT_RX_PRESENTL                |  |  |

| Function | Mask when reading                            | 0 = Interrupt<br>1 = No Interrupt | Mask when reading | 0 = Present<br>1 = Not Present |  |  |

## 1.5.1.1 OPT\_RX\_INTL

This bit indicates an interrupt from the optical receive module. A "1" indicates no interrupt; a "0" indicates an interrupt is present. Refer to the Samtec FireFly data sheet for interpretation of this interrupt.

#### 1.5.1.2 OPT\_RX\_PRESENTL

This bit indicates the presence of the optical receive module on this connector. A "1" indicates that it is not present; a "0" indicates the module is present.

## **1.5 PCA9535 Port A – Optical Receive** (continued)

## 1.5.2 Port A, Register 2 – Output Data (WRITE ONLY)

| Table 1–2: PCA Register 2: Port A Data Output |             |                      |                                 |            |  |

|-----------------------------------------------|-------------|----------------------|---------------------------------|------------|--|

|                                               | 7 – 3       | 2                    | 1                               | 0          |  |

| Bit Name                                      | NOT USED    | OPT_RX_RESETL        | OPT_RX_SELECTL                  | NOT USED   |  |

| Function                                      | Write zeros | 0 = Reset<br>1 = Run | 0 = Select<br>1 = Do not select | Write zero |  |

## 1.5.2.1 OPT\_RX\_RESETL

This bit resets the optical receive module. A "0" holds the device in a reset state, a "1" allows it to run.

## 1.5.2.2 OPT\_RX\_SELECTL

This bit selects the serial interface pins of the optical receive module (SDA and SCL). A "0" enables the optical receive serial interface and allows this module to communicate on the TWSI bus; a "1" disables the TWSI interface.

## **1.5.3** Port A, Register 4 – Polarity Control

Input data inversion on the Model 7807 is not used. Since the power–on default state of all bits is "0", this register does not require programming

## 1.5.4 Port A, Register 6 – I/O Control

To configure a port pin as an output, set the corresponding register bit to "0". To configure a pin as an input, set the register bit to "1". The following shows the bit settings for Port A, where bits 3 and 0 are the only input pins.

|          | Table 1–3: PCA Register 6: Port A I/O Control |   |   |   |   |   |   |   |

|----------|-----------------------------------------------|---|---|---|---|---|---|---|

|          | 7                                             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Function | 0                                             | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

## **1.6 PCA9535 Port B – Optical Transmit**

PCA9535 Port B is connected to the optical transmit module control connector **J27**, and is used to program the active interface and read status from it. Port B is accessed and controlled using PCA9535 internal registers 1, 3, 5, and 7, as follows:

- Register 1 Data input from Port B

- Register 3 Data output to Port B

- Register 5 Invert input data from Port B

- Register 7 I/O control of Port B

## **1.6.1 Port B, Register 1 – Input Data (READ ONLY)**

|          | Table 1–4: PCA Register 1: Port B Data Input |                                   |                   |                                |  |  |

|----------|----------------------------------------------|-----------------------------------|-------------------|--------------------------------|--|--|

|          | 7 – 4                                        | 3                                 | 2 – 1             | 0                              |  |  |

| Bit Name | NOT USED                                     | OPT_TX_INTL                       | NOT USED          | OPT_TX_PRESENTL                |  |  |

| Function | Mask when reading                            | 0 = Interrupt<br>1 = No Interrupt | Mask when reading | 0 = Present<br>1 = Not Present |  |  |

## 1.6.1.1 OPT\_TX\_INTL

This bit indicates an interrupt from the optical transmit module. A "1" indicates no interrupt; a "0" indicates an interrupt is present. Refer to the Samtec FireFly data sheet for interpretation of this interrupt.

1.6.1.2 OPT\_TX\_PRESENTL

This bit indicates the presence of an optical transmit module on this connector. A "1" indicates that it is not present; a "0" indicates the module is present.

## **1.6 PCA9535 Port B – Optical Transmit** (continued)

## **1.6.2 Port B, Register 3 – Output Data (WRITE ONLY)**

| Table 1–5: PCA Register 3: Port B Data Output |             |                      |                                 |            |

|-----------------------------------------------|-------------|----------------------|---------------------------------|------------|

|                                               | 7 – 3       | 2                    | 1                               | 0          |

| Bit Name                                      | NOT USED    | OPT_TX_RESETL        | OPT_TX_SELECTL                  | NOT USED   |

| Function                                      | Write zeros | 0 = Reset<br>1 = Run | 0 = Select<br>1 = Do not select | Write zero |

## 1.6.2.1 OPT\_TX\_RESETL

This resets the optical transmit module. A "0" holds the device in a reset state, a "1" allows it to run.

## 1.6.2.2 OPT\_TX\_SELECTL

This bit selects the serial interface pins of the optical transmit module (SDA and SCL). A "0" enables the optical transmit serial interface and allows this module to communicate on the TWSI bus; a "1" disables the TWSI interface.

## **1.6.3 Port B, Register 5 – Polarity Control**

Input data inversion on the Model 7807 is not used. Since the power–on default state of all bits is "0", this register does not require programming

## 1.6.4 Port B, Register 7 – I/O Control

To configure a port pin as an output, set the corresponding register bit to "0". To configure a pin as an input, set the register bit to "1". The following shows the bit settings for Port B, where bits 3 and 0 are the only input pins.

|          | Table 1–6: PCA Register 7: Port B I/O Control |   |   |   |   |   |   |   |

|----------|-----------------------------------------------|---|---|---|---|---|---|---|

|          | 7                                             | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Function | 0                                             | 0 | 0 | 0 | 1 | 0 | 0 | 1 |

# Appendix A: Phillips Semiconductors Corporation, PCA9535 Data Sheet

## A.1 Introduction

The following pages are a reprint of the Phillips Semiconductors Corporation, PCA9535 16–bit I<sup>2</sup>C and SMBus I/O port Data Sheet.

This page is intentionally blank

## INTEGRATED CIRCUITS

Product data

2003 Jun 27

PCA9535

#### FEATURES

- Operating power supply voltage range of 2.3 V-5.5 V

- 5 V tolerant I/Os

- Polarity inversion register

- Active LOW interrupt output

- Low stand-by current

- Noise filter on SCL/SDA inputs

- No glitch on power-up

- Internal power-on reset

- 16 I/O pins which default to 16 inputs

- 0 to 400 kHz clock frequency

- ESD protection exceeds 2000 V HBM per JESD22-A114, 200 V MM per JESD22-A115, and 1000 V CDM per JESD22-C101

- Latch-up testing is done to JESDEC Standard JESD78 which exceeds 100 mA

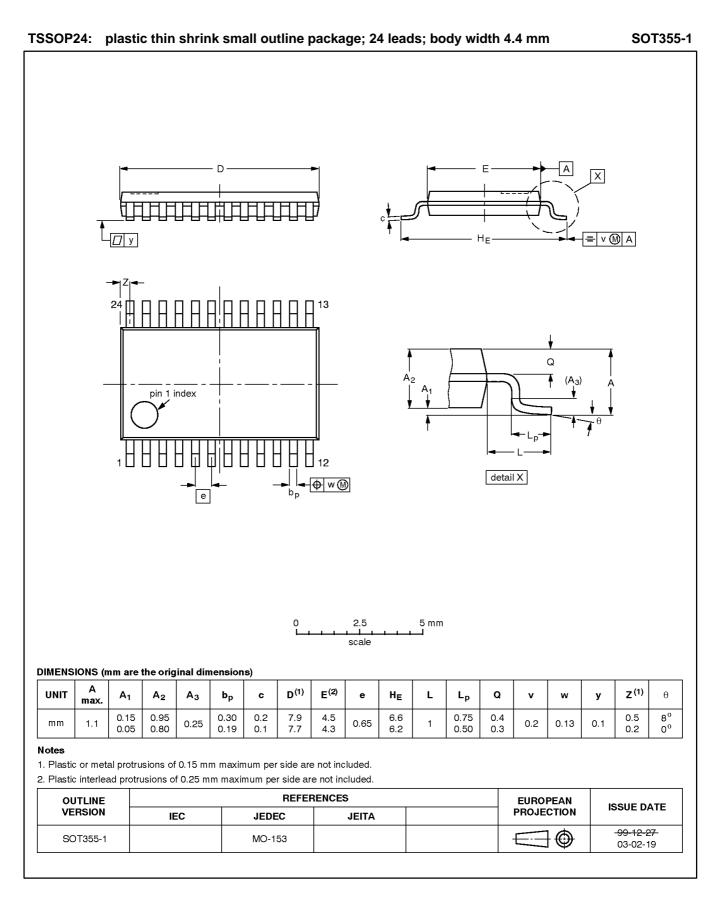

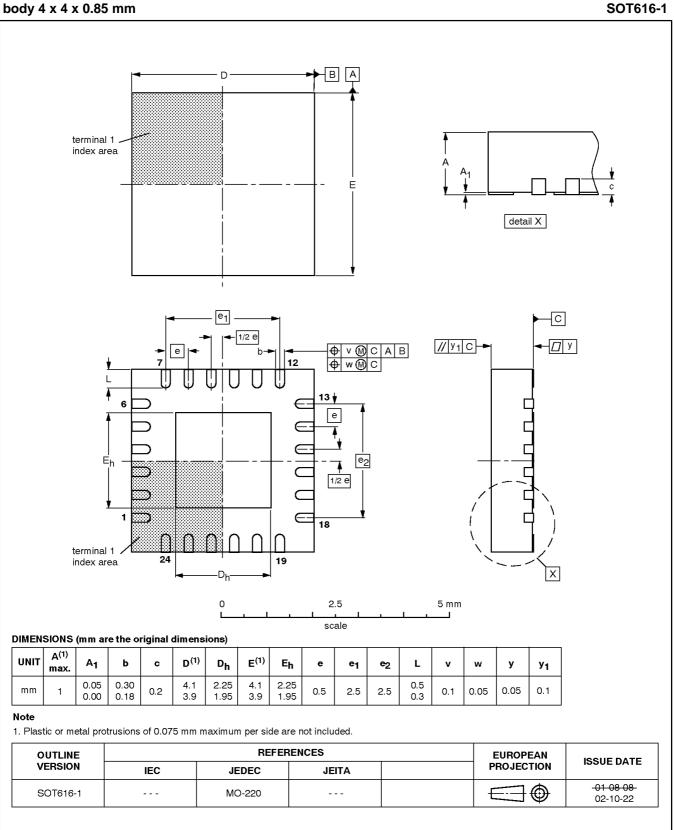

- Offered in three different packages: SO24, TSSOP24, and HVQFN24

#### DESCRIPTION

The PCA9535 is a 24-pin CMOS device that provide 16 bits of General Purpose parallel Input/Output (GPIO) expansion for

#### **ORDERING INFORMATION**

| PACKAGES             | TEMPERATURE RANGE | ORDER CODE | TOPSIDE MARK | DRAWING NUMBER |

|----------------------|-------------------|------------|--------------|----------------|

| 24-Pin Plastic SO    | -40 to +85 °C     | PCA9535D   | PCA9535D     | SOT137-1       |

| 24-Pin Plastic TSSOP | -40 to +85 °C     | PCA9535PW  | PCA9535PW    | SOT355-1       |

| 24-Pin Plastic HVQFN | -40 to +85 °C     | PCA9535BS  | 9535         | SOT616-1       |

Standard packing quantities and other packing data are available at www.philipslogic.com/packaging.

I<sup>2</sup>C is a trademark of Philips Semiconductors Corporation.

SMBus as specified by the Smart Battery System Implementers Forum is a derivative of the Philips I<sup>2</sup>C patent.

I<sup>2</sup>C/SMBus applications and was developed to enhance the Philips family of I<sup>2</sup>C I/O expanders. The improvements include higher drive capability, 5 V I/O tolerance, lower supply current, individual I/O configuration, and smaller packaging. I/O expanders provide a simple solution when additional I/O is needed for ACPI power switches, sensors, pushbuttons, LEDs, fans, etc.

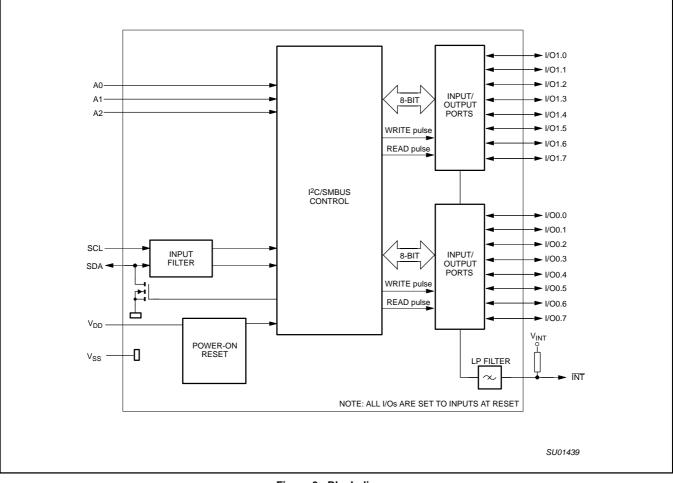

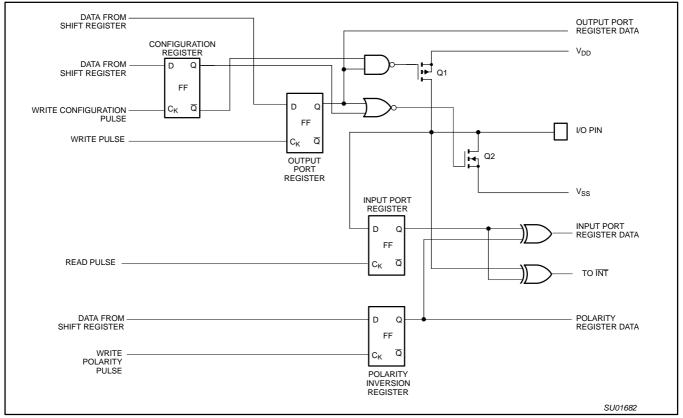

The PCA9535 consist of two 8-bit Configuration (Input or Output selection); Input, Output and Polarity inversion (Active HIGH or Active LOW operation) registers. The system master can enable the I/Os as either inputs or outputs by writing to the I/O configuration bits. The data for each Input or Output is kept in the corresponding Input or Output register. The polarity of the read register can be inverted with the Polarity Inversion Register. All registers can be read by the system master. Although pin-to-pin and I<sup>2</sup>C address compatible with the PCF8575, software changes are required due to the enhancements and are discussed in Application Note AN469.

The PCA9535 is identical to the PCA9555 except for the removal of the internal I/O pull-up resistor which greatly reduces power consumption when the I/Os are held LOW.

The PCA9535 open-drain interrupt output is activated when any input state differs from its corresponding input port register state and is used to indicate to the system master that an input state has changed. The power-on reset sets the registers to their default values and initializes the device state machine.

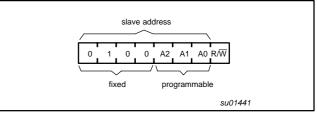

Three hardware pins (A0, A1, A2) vary the fixed  $I^2C$  address and allow up to eight devices to share the same  $I^2C/SMBus$ . The fixed  $I^2C$  address of the PCA9535 is the same as the PCA9554 allowing up to eight of these devices in any combination to share the same  $I^2C/SMBus$ .

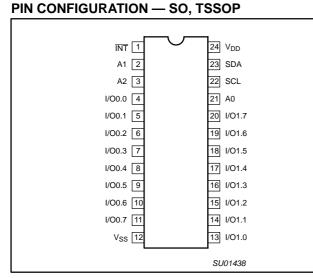

## PCA9535

Figure 1. Pin configuration — SO, TSSOP

#### **PIN DESCRIPTION**

| SO,<br>TSSOP<br>PIN<br>NUMBER | HVQFN<br>PIN<br>NUMBER | SYMBOL          | FUNCTION                      |

|-------------------------------|------------------------|-----------------|-------------------------------|

| 1                             | 22                     | INT             | Interrupt output (open drain) |

| 2                             | 23                     | A1              | Address input 1               |

| 3                             | 24                     | A2              | Address input 2               |

| 4-11                          | 1-8                    | I/O0.0-I/O0.7   | I/O0.0 to I/O0.7              |

| 12                            | 9                      | V <sub>SS</sub> | Supply ground                 |

| 13-20                         | 10-17                  | I/01.0-I/01.7   | I/O1.0 to I/O1.7              |

| 21                            | 18                     | A0              | Address input 0               |

| 22                            | 19                     | SCL             | Serial clock line             |

| 23                            | 20                     | SDA             | Serial data line              |

| 24                            | 21                     | V <sub>DD</sub> | Supply voltage                |

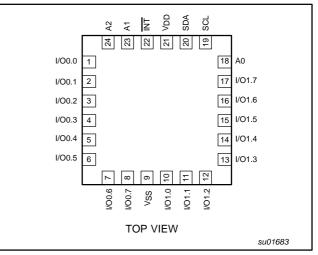

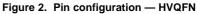

#### **PIN CONFIGURATION — HVQFN**

## PCA9535

#### **BLOCK DIAGRAM**

Figure 3. Block diagram

#### SIMPLIFIED SCHEMATIC OF I/Os

NOTE: At Power-on Reset, all registers return to default values.

Figure 4. Simplified schematic of I/Os

#### I/O port

When an I/O is configured as an input, FETs Q1 and Q2 are off, creating a high impedance input. The input voltage may be raised above  $V_{DD}$  to a maximum of 5.5 V.

If the I/O is configured as an output, then either Q1 or Q2 is on, depending on the state of the Output Port register. Care should be exercised if an external voltage is applied to an I/O configured as an output because of the low impedance path that exists between the pin and either V<sub>DD</sub> or V<sub>SS</sub>.

## PCA9535

## PCA9535

#### REGISTERS

#### **Command Byte**

| Command | Register                  |

|---------|---------------------------|

| 0       | Input port 0              |

| 1       | Input port 1              |

| 2       | Output port 0             |

| 3       | Output port 1             |

| 4       | Polarity inversion port 0 |

| 5       | Polarity inversion port 1 |

| 6       | Configuration port 0      |

| 7       | Configuration port 1      |

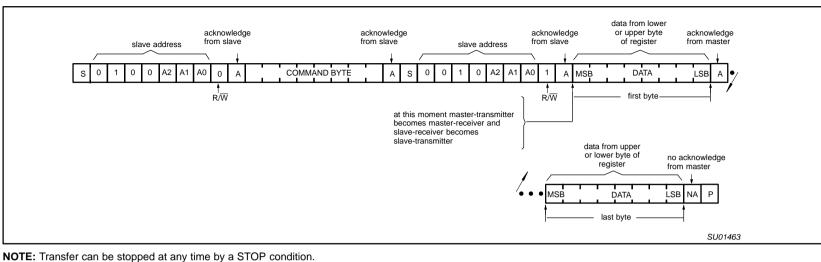

The command byte is the first byte to follow the address byte during a write transmission. It is used as a pointer to determine which of the following registers will be written or read.

#### Registers 0 and 1 — Input Port Registers

This register is an input-only port. It reflects the incoming logic levels of the pins, regardless of whether the pin is defined as an input or an output by Register 3. Writes to this register have no effect.

#### Registers 2 and 3 — Output Port Registers

| bit     | O0.7 | O0.6 | O0.5 | O0.4 | O0.3 | O0.2 | O0.1 | O0.0 |

|---------|------|------|------|------|------|------|------|------|

| default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| bit     | 01.7 | 01.6 | 01.5 | 01.4 | 01.3 | 01.2 | 01.1 | 01.0 |

| default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

This register is an output-only port. It reflects the outgoing logic levels of the pins defined as outputs by Register 6 and 7. Bit values in this register have no effect on pins defined as inputs. In turn, reads from this register reflect the value that is in the flip-flop controlling the output selection, NOT the actual pin value.

#### Registers 4 and 5 — Polarity Inversion Registers

| bit     | N0.7 | N0.6 | N0.5 | N0.4 | N0.3 | N0.2 | N0.1 | N0.0 |

|---------|------|------|------|------|------|------|------|------|

| default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

| bit     | N1.7 | N1.6 | N1.5 | N1.4 | N1.3 | N1.2 | N1.1 | N1.0 |

| default | 0    | 0    | 0    | 0    | 0    | 0    | 0    | 0    |

This register allows the user to invert the polarity of the Input Port register data. If a bit in this register is set (written with '1'), the Input Port data polarity is inverted. If a bit in this register is cleared (written with a '0'), the Input Port data polarity is retained.

#### Registers 6 and 7 — Configuration Registers

| bit     | C0.7 | C0.6 | C0.5 | C0.4 | C0.3 | C0.2 | C0.1 | C0.0 |

|---------|------|------|------|------|------|------|------|------|

| default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

| bit     | C1.7 | C1.6 | C1.5 | C1.4 | C1.3 | C1.2 | C1.1 | C1.0 |

| default | 1    | 1    | 1    | 1    | 1    | 1    | 1    | 1    |

This register configures the directions of the I/O pins. If a bit in this register is set (written with '1'), the corresponding port pin is enabled as an input with high impedance output driver. If a bit in this register is cleared (written with '0'), the corresponding port pin is enabled as an output. At reset the device's ports are inputs.

#### **POWER-ON RESET**

When power is applied to  $V_{DD}$ , an internal power-on reset holds the PCA9535 in a reset state until  $V_{DD}$  has reached  $V_{POR}$ . At that point, the reset condition is released and the PCA9535 registers and SMBus state machine will initialize to their default states.

#### **DEVICE ADDRESS**

Figure 5. PCA9535 address

#### **BUS TRANSACTIONS**

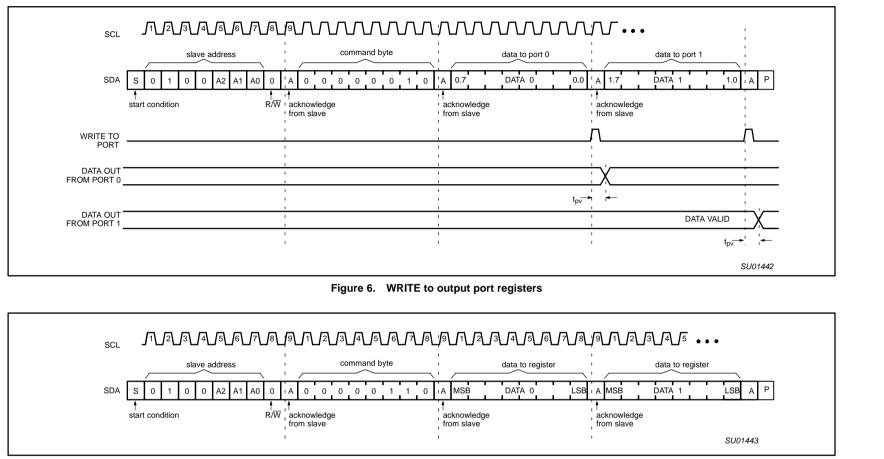

#### Writing to the port registers

Data is transmitted to the PCA9535 by sending the device address and setting the least significant bit to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register will receive the data following the command byte.

The eight registers within the PCA9535 are configured to operate as four register pairs. The four pairs are Input Ports, Output Ports, Polarity Inversion Ports, and Configuration Ports. After sending data to one register, the next data byte will be sent to the other register in the pair (see Figures 6 and 7). For example, if the first byte is sent to Output Port (register 3), then the next byte will be stored in Output Port 0 (register 2). There is no limitation on the number of data bytes sent in one write transmission. In this way, each 8-bit register may be updated independently of the other registers.

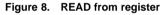

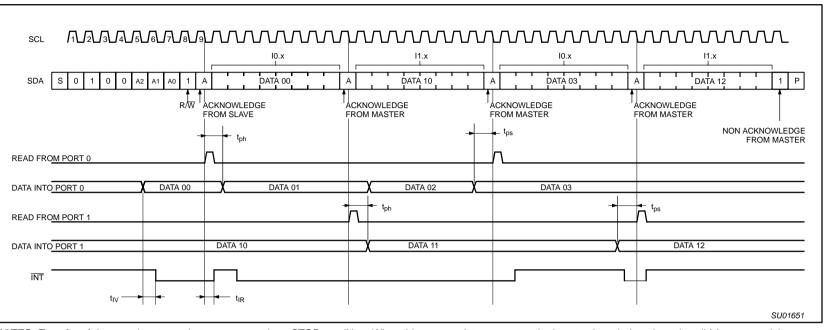

#### Reading the port registers

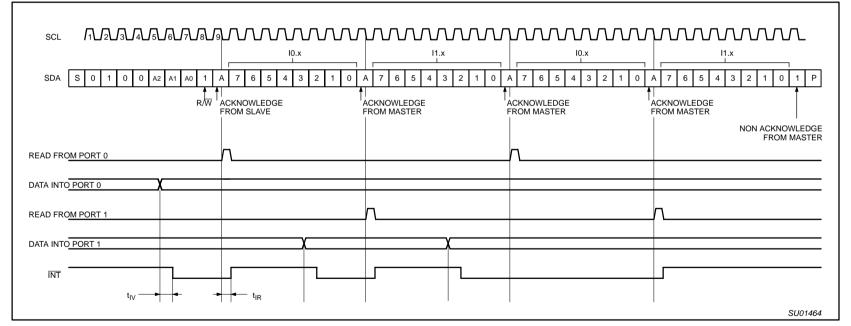

In order to read data from the PCA9535, the bus master must first send the PCA9535 address with the least significant bit set to a logic 0 (see Figure 5 for device address). The command byte is sent after the address and determines which register will be accessed. After a restart, the device address is sent again but this time, the least significant bit is set to a logic 1. Data from the register defined by the command byte will then be sent by the PCA9535 (see Figures 8, 9, and 10). Data is clocked into the register on the falling edge of the acknowledge clock pulse. After the first byte is read, additional bytes may be read but the data will now reflect the information in the other register in the pair. For example, if you read Input Port 1, then the next byte read would be Input Port 0. There is no limitation on the number of data bytes received in one read transmission but the final byte received, the bus master must not acknowledge the data.

#### **Interrupt Output**

The open-drain interrupt output is activated when one of the port pins change state and the pin is configured as an input. The interrupt is deactivated when the input returns to its previous state or the input port register is read (see Figure 9). A pin configured as an output cannot cause an interrupt. Since each 8-bit port is read independently, the interrupt caused by Port 0 will not be cleared by a read of Port 1 or the other way around.

Note that changing an I/O from an output to an input may cause a false interrupt to occur if the state of the pin does not match the contents of the Input Port register.

16-bit I<sup>2</sup>C

and

Product data

Figure 7. WRITE to configuration registers

~

ω

**NOTES:** Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to 00 (read input port port register).

Figure 9. READ input port register — scenario 1

16-bit I<sup>2</sup>C

and

SMBus,

low power I/O port with interrupt

PCA9535

Product data

**NOTES:** Transfer of data can be stopped at any moment by a STOP condition. When this occurs, data present at the latest acknowledge phase is valid (output mode). It is assumed that the command byte has previously been set to 00 (read input port port register).

Figure 10. READ input port register — scenario 2

16-bit I<sup>2</sup>C

and

SMBus,

low power I/O

port with interrupt

PCA9535

Product data

## PCA9535

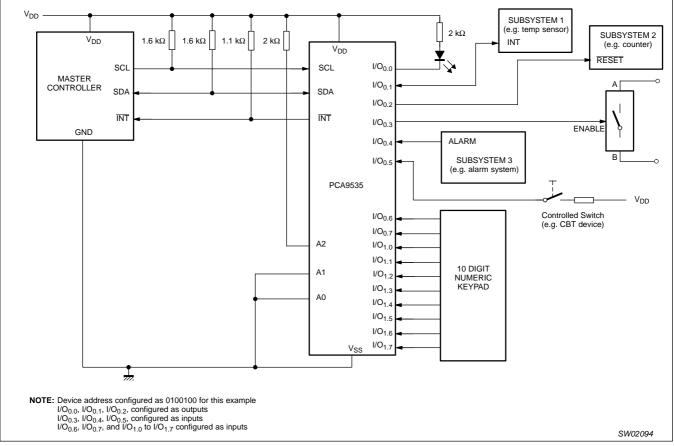

#### **TYPICAL APPLICATION**

Figure 11. Typical application

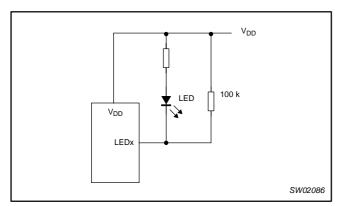

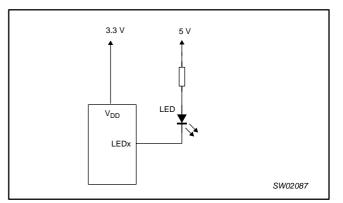

#### Minimizing I<sub>DD</sub> when the I/O is used to control LEDs

When the I/Os are used to control LEDs, they are normally connected to  $V_{DD}$  through a resistor as shown in Figure 11. Since the LED acts as a diode, when the LED is off the I/O  $V_{IN}$  is about 1.2 V less than  $V_{DD}$ . The supply current,  $I_{DD}$ , increases as  $V_{IN}$  becomes lower than  $V_{DD}$  and is specified as  $\Delta I_{DD}$  in the DC characteristics table.

Designs needing to minimize current consumption, such as battery power applications, should consider maintaining the I/O pins greater than or equal to  $V_{DD}$  when the LED is off. Figure 12 shows a high value resistor in parallel with the LED. Figure 13 shows  $V_{DD}$  less than the LED supply voltage by at least 1.2 V. Both of these methods maintain the I/O  $V_{IN}$  at or above  $V_{DD}$  and prevents additional supply current consumption when the LED is off.

Figure 12. High value resistor in parallel with the LED

Figure 13. Device supplied by a lower voltage

## PCA9535

#### **ABSOLUTE MAXIMUM RATINGS**

In accordance with the Absolute Maximum Rating System (IEC 134)

| SYMBOL           | PARAMETER                     | CONDITIONS | MIN                   | MAX  | UNIT |

|------------------|-------------------------------|------------|-----------------------|------|------|

| V <sub>DD</sub>  | Supply voltage                |            | -0.5                  | 6.0  | V    |

| V <sub>I/O</sub> | DC input current on an I/O    |            | V <sub>SS</sub> - 0.5 | 6    | V    |

| I <sub>I/O</sub> | DC output current on an I/O   |            | —                     | ± 50 | mA   |

| l                | DC input current              |            | —                     | ± 20 | mA   |

| I <sub>DD</sub>  | Supply current                |            | —                     | 160  | mA   |

| I <sub>SS</sub>  | Supply current                |            | —                     | 200  | mA   |

| P <sub>tot</sub> | Total power dissipation       |            | —                     | 200  | mW   |

| T <sub>stg</sub> | Storage temperature range     |            | -65                   | +150 | °C   |

| T <sub>amb</sub> | Operating ambient temperature |            | -40                   | +85  | °C   |

## PCA9535

#### HANDLING

Inputs and outputs are protected against electrostatic discharge in normal handling. However, to be totally safe, it is desirable to take precautions appropriate to handling MOS devices. Advice can be found in Data Handbook IC24 under "Handling MOS devices".

#### **DC CHARACTERISTICS**

$V_{DD}$  = 2.3 to 5.5 V;  $V_{SS}$  = 0 V;  $T_{amb}$  = -40 to +85  $^\circ C$ ; unless otherwise specified.

| SYMBOL            | PARAMETER                 | CONDITIONS                                                                                          | MIN                 | TYP   | MAX                 | UNIT |

|-------------------|---------------------------|-----------------------------------------------------------------------------------------------------|---------------------|-------|---------------------|------|

| Supplies          | •                         | ·                                                                                                   | -                   |       | -                   |      |

| $V_{DD}$          | Supply voltage            |                                                                                                     | 2.3                 | —     | 5.5                 | V    |

| I <sub>DD</sub>   | Supply current            | Operating mode; $V_{DD}$ = 5.5 V; no load; $f_{SCL}$ = 100 kHz; I/O = inputs                        | -                   | 135   | 200                 | μA   |

| I <sub>stbl</sub> | Standby current           | Standby mode; $V_{DD}$ = 5.5 V; no load; $V_I$ = $V_{SS}$ ; f <sub>SCL</sub> = 0 kHz; I/O = inputs  | -                   | 0.25  | 1                   | μΑ   |

| I <sub>stbh</sub> | Standby current           | Standby mode; $V_{DD} = 5.5 V$ ; no load; $V_I = V_{DD}$ ; $f_{SCL} = 0 \text{ kHz}$ ; I/O = inputs | _                   | 0.25  | 1                   | μΑ   |

| V <sub>POR</sub>  | Power-on reset voltage    | No load; $V_I = V_{DD}$ or $V_{SS}$                                                                 | —                   | 1.5   | 1.65                | V    |

|                   | input/output SDA          | •                                                                                                   | •                   |       |                     |      |

| V <sub>IL</sub>   | LOW-level input voltage   |                                                                                                     | -0.5                | _     | 0.3 V <sub>DD</sub> | V    |

| VIH               | HIGH-level input voltage  |                                                                                                     | 0.7 V <sub>DD</sub> | _     | 5.5                 | V    |

| I <sub>OL</sub>   | LOW-level output current  | $V_{OL} = 0.4V$                                                                                     | 3                   | _     | —                   | mA   |

| ١ <sub>L</sub>    | Leakage current           | $V_{I} = V_{DD} = V_{SS}$                                                                           | -1                  | _     | +1                  | μA   |

| Cl                | Input capacitance         | $V_{I} = V_{SS}$                                                                                    | —                   | 6     | 10                  | pF   |

| I/Os              | •                         | •                                                                                                   | •                   |       |                     |      |

| V <sub>IL</sub>   | LOW-level input voltage   |                                                                                                     | -0.5                | _     | 0.8                 | V    |

| VIH               | HIGH-level input voltage  |                                                                                                     | 2.0                 | _     | 5.5                 | V    |

|                   | LOW-level output current  | V <sub>OL</sub> = 0.5 V; V <sub>DD</sub> = 2.3-5.5 V; Note 1                                        | 8                   | 8-20  | —                   | mA   |

| I <sub>OL</sub>   |                           | V <sub>OL</sub> = 0.7 V; V <sub>DD</sub> = 2.3-5.5 V; Note 1                                        | 10                  | 10-24 | —                   | mA   |

|                   | HIGH-level output voltage | I <sub>OH</sub> = -8 mA; V <sub>DD</sub> = 2.3 V; Note 2                                            | 1.8                 | _     | —                   | V    |

|                   |                           | I <sub>OH</sub> = -10 mA; V <sub>DD</sub> = 2.3 V; Note 2                                           | 1.7                 | _     | _                   | V    |

| M                 |                           | I <sub>OH</sub> = -8 mA; V <sub>DD</sub> = 3.0 V; Note 2                                            | 2.6                 |       | —                   | V    |

| V <sub>OH</sub>   |                           | I <sub>OH</sub> = -10 mA; V <sub>DD</sub> = 3.0 V; Note 2                                           | 2.5                 |       | —                   | V    |

|                   |                           | $I_{OH}$ = -8 mA; $V_{DD}$ = 4.75 V; Note 2                                                         | 4.1                 |       | —                   | V    |

|                   |                           | $I_{OH}$ = -10 mA; $V_{DD}$ = 4.75 V; Note 2                                                        | 4.0                 | _     | —                   | V    |

| I <sub>IH</sub>   | Input leakage current     | $V_{DD} = 5.5 \text{ V}; \text{ V}_{I} = V_{DD}$                                                    | —                   |       | 1                   | μA   |

| ۱ <sub>IL</sub>   | Input leakage current     | $V_{DD} = 5.5 \text{ V}; \text{ V}_{I} = \text{V}_{SS}$                                             | —                   | _     | -1                  | μA   |

| Cl                | Input capacitance         |                                                                                                     | —                   | 3.7   | 5                   | pF   |

| CO                | Output capacitance        |                                                                                                     | _                   | 3.7   | 5                   | pF   |

| Interrupt IN      | Ť                         |                                                                                                     | -                   | -     | -                   |      |

| I <sub>OL</sub>   | LOW-level output current  | V <sub>OL</sub> = 0.4 V                                                                             | 3                   |       | _                   | mA   |

| Select Inpu       | ts A0, A1, A2             |                                                                                                     |                     |       |                     |      |

| V <sub>IL</sub>   | LOW-level input voltage   |                                                                                                     | -0.5                | _     | 0.8                 | V    |

| VIH               | HIGH-level input voltage  |                                                                                                     | 2.0                 | —     | 5.5                 | V    |

| ILI               | Input leakage current     |                                                                                                     | -1                  | _     | 1                   | μA   |

NOTES:

1. The total current sunk by all I/Os must be limited to 200 mA.

2. The total current sourced by all I/Os must be limited to 160 mA.

## PCA9535

Figure 14. Definition of timing

#### **AC CHARACTERISTICS**

| SYMBOL              | PARAMETER                                                          |     | RD MODE<br>BUS | FAST M<br>I <sup>2</sup> C BI       | UNITS |     |

|---------------------|--------------------------------------------------------------------|-----|----------------|-------------------------------------|-------|-----|

|                     |                                                                    | MIN | MAX            | MIN                                 | MAX   | 1   |

| fscl                | Operating frequency                                                | 0   | 100            | 0                                   | 400   | kHz |

| t <sub>BUF</sub>    | Bus free time between STOP and START conditions                    | 4.7 | —              | 1.3                                 | _     | μs  |

| t <sub>HD;STA</sub> | Hold time after (repeated) START condition                         | 4.0 | —              | 0.6                                 | _     | μs  |

| t <sub>SU;STA</sub> | Repeated START condition setup time                                | 4.7 | —              | 0.6                                 | _     | μs  |

| t <sub>su;sтo</sub> | Set-up time for STOP condition                                     | 4.0 | —              | 0.6                                 | _     | μs  |

| t <sub>VD;ACK</sub> | Valid time of ACK condition <sup>2</sup>                           | 0.3 | 3.45           | 0.1                                 | 0.9   | μs  |

| t <sub>HD;DAT</sub> | Data in hold time                                                  | 0   | —              | 0                                   | _     | ns  |

| t <sub>VD;DAT</sub> | Data out valid time <sup>3</sup>                                   | 300 | —              | 50                                  | _     | ns  |

| t <sub>SU;DAT</sub> | Data set-up time                                                   | 250 | —              | 100                                 | _     | ns  |

| t <sub>LOW</sub>    | Clock LOW period                                                   | 4.7 | —              | 1.3                                 | _     | μs  |

| t <sub>HIGH</sub>   | Clock HIGH period                                                  | 4.0 | —              | 0.6                                 | _     | μs  |

| t <sub>F</sub>      | Clock/Data fall time                                               | _   | 300            | 20 + 0.1C <sub>b</sub> <sup>1</sup> | 300   | ns  |

| t <sub>R</sub>      | Clock/Data rise time                                               | _   | 1000           | 20 + 0.1C <sub>b</sub> <sup>1</sup> | 300   | ns  |

| t <sub>SP</sub>     | Pulse width of spikes that must be suppressed by the input filters | -   | 50             | —                                   | 50    | ns  |

| Port Timing         |                                                                    |     | -              |                                     |       |     |

| t <sub>PV</sub>     | Output data valid                                                  | _   | 200            |                                     | 200   | ns  |

| t <sub>PS</sub>     | Input data set-up time                                             | 150 | —              | 150                                 | _     | ns  |

| t <sub>PH</sub>     | Input data hold time                                               | 1   | —              | 1                                   |       | μs  |

| Interrupt Ti        | ming                                                               |     |                |                                     |       |     |

| t <sub>IV</sub>     | Interrupt valid                                                    | —   | 4              | —                                   | 4     | μs  |

| t <sub>IR</sub>     | Interrupt reset                                                    | _   | 4              | _                                   | 4     | μs  |

NOTES:

1.  $C_b$  = total capacitance of one bus line in pF. 2.  $t_{VD;ACK}$  = time for Acknowledgement signal from SCL LOW to SDA (out) LOW. 3.  $t_{VD;DAT}$  = minimum time for SDA data out to be valid following SCL LOW. 4.  $t_{PV}$  measured from 0.7V<sub>DD</sub> on SCL to 50% I/O output.

Figure 15. t<sub>PV</sub> set-up conditions

## PCA9535

PCA9535

# 16-bit I<sup>2</sup>C and SMBus, low power I/O port with interrupt

#### SO24: plastic small outline package; 24 leads; body width 7.5 mm SOT137-1 А Х = v (M) A Ду 13 Q pin 1 index 🛛 12 detail X e < + ♥ w ₪ bp 10 mm 5 0 scale DIMENSIONS (inch dimensions are derived from the original mm dimensions) Α E<sup>(1)</sup> D <sup>(1)</sup> z<sup>(1)</sup> UNIT Lp θ A<sub>1</sub> $A_2$ A<sub>3</sub> bp С ΗE L Q v w У е max. 0.3 2.45 0.49 0.32 15.6 7.6 10.65 0.9 1.1 1.1 2.65 mm 0.25 1.27 1.4 0.25 0.25 0.1 2.25 10.00 1.0 0.4 0.1 0.36 0.23 15.2 7.4 0.4 8° 0<sup>0</sup> 0.012 0.096 0.019 0.013 0.61 0.30 0.419 0.043 0.043 0.035 0.05 inches 0.1 0.004 0.01 0.055 0.01 0.01 0.016 0.004 0.089 0.014 0.009 0.60 0.29 0.394 0.016 0.039 Note 1. Plastic or metal protrusions of 0.15 mm (0.006 inch) maximum per side are not included. REFERENCES OUTLINE EUROPEAN **ISSUE DATE** VERSION PROJECTION IEC JEDEC JEITA -99-12-27 ۲ SOT137-1 075E05 MS-013 E 03-02-19

#### 15

## PCA9535

PCA9535

# 16-bit I<sup>2</sup>C and SMBus, low power I/O port with interrupt

# HVQFN24: plastic thermal enhanced very thin quad flat package; no leads; 24 terminals; body 4 x 4 x 0.85 mm

## PCA9535

#### **REVISION HISTORY**

| Rev | Date     | Description                                                                              |

|-----|----------|------------------------------------------------------------------------------------------|

| _1  | 20030627 | Product data (9397 750 11681); ECN 853-2430 30019 dated 11 June 2003.<br>Initial version |

PCA9535

## 16-bit I<sup>2</sup>C and SMBus, low power I/O port with interrupt

Purchase of Philips I<sup>2</sup>C components conveys a license under the Philips' I<sup>2</sup>C patent to use the components in the I<sup>2</sup>C system provided the system conforms to the I<sup>2</sup>C specifications defined by Philips. This specification can be ordered using the code 9398 393 40011.

#### Data sheet status

| Level | Data sheet status <sup>[1]</sup> | Product<br>status <sup>[2] [3]</sup> | Definitions                                                                                                                                                                                                                                                                                    |

|-------|----------------------------------|--------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I     | Objective data                   | Development                          | This data sheet contains data from the objective specification for product development.<br>Philips Semiconductors reserves the right to change the specification in any manner without notice.                                                                                                 |

| II    | Preliminary data                 | Qualification                        | This data sheet contains data from the preliminary specification. Supplementary data will be published at a later date. Philips Semiconductors reserves the right to change the specification without notice, in order to improve the design and supply the best possible product.             |

| 111   | Product data                     | Production                           | This data sheet contains data from the product specification. Philips Semiconductors reserves the right to make changes at any time in order to improve the design, manufacturing and supply. Relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). |

[1] Please consult the most recently issued data sheet before initiating or completing a design.

[2] The product status of the device(s) described in this data sheet may have changed since this data sheet was published. The latest information is available on the Internet at URL http://www.semiconductors.philips.com.

[3] For data sheets describing multiple type numbers, the highest-level product status determines the data sheet status.

#### Definitions

Short-form specification — The data in a short-form specification is extracted from a full data sheet with the same type number and title. For detailed information see the relevant data sheet or data handbook.

Limiting values definition — Limiting values given are in accordance with the Absolute Maximum Rating System (IEC 60134). Stress above one or more of the limiting values may cause permanent damage to the device. These are stress ratings only and operation of the device at these or at any other conditions above those given in the Characteristics sections of the specification is not implied. Exposure to limiting values for extended periods may affect device reliability.

**Application information** — Applications that are described herein for any of these products are for illustrative purposes only. Philips Semiconductors make no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

#### Disclaimers

Life support — These products are not designed for use in life support appliances, devices, or systems where malfunction of these products can reasonably be expected to result in personal injury. Philips Semiconductors customers using or selling these products for use in such applications do so at their own risk and agree to fully indemnify Philips Semiconductors for any damages resulting from such application.

Right to make changes — Philips Semiconductors reserves the right to make changes in the products—including circuits, standard cells, and/or software—described or contained herein in order to improve design and/or performance. When the product is in full production (status 'Production'), relevant changes will be communicated via a Customer Product/Process Change Notification (CPCN). Philips Semiconductors assumes no responsibility or liability for the use of any of these products, conveys no license or title under any patent, copyright, or mask work right to these products, and makes no representations or warranties that these products are free from patent, copyright, or mask work right infringement, unless otherwise specified.

#### **Contact information**

For additional information please visit http://www.semiconductors.philips.com. Fax: +31 40 27 24825

sales.addresses@www.semiconductors.philips.com.

For sales offices addresses send e-mail to:

© Koninklijke Philips Electronics N.V. 2003 All rights reserved. Printed in U.S.A.

Date of release: 06-03

9397 750 11681

Let's make things better.

Document order number:

HILIPS

This page is intentionally blank

# Appendix B: Samtec Inc, FireFly™ Optical User Manual

## B.1 Introduction

The following pages are a reprint of the Samtec Inc, FireFly<sup>™</sup> Optical User Manual.

This page is intentionally blank

# FireFly<sup>™</sup> Optical User Manual

Revision D03 - January, 2014

## **COPYRIGHTS, TRADEMARKS AND PATENTS**

Product names used herein are trademarks of their respective owners. All information and material in this publication are property of Samtec, Inc. All related rights are reserved. Samtec, Inc. does not authorize customers to make copies of the content for any use.

#### Terms of Use

Use of this publication is limited to viewing the pages for evaluation or purchase. No permission is granted to the user to copy, print, distribute, transmit, display in public, or modify the contents of this document in any way.

#### **Disclaimer**

The information in this publication may change without notice. All materials published here are "As Is" and without implied or express warranties. Samtec, Inc. does not warrant that this publication will be without error, or that defects will be corrected. Samtec, Inc. makes every effort to present our customers an excellent and useful publication, but we do not warrant or represent the use of the materials here in terms of their accuracy, reliability or otherwise. Therefore, you agree that all access and use of this publication's content is at your own risk.

#### **Patents**

Patents: 8588562 and 858856. Additional Patents pending.

NEITHER SAMTEC, INC. NOR ANY PARTY INVOLVED IN CREATING, PRODUCING, OR DELIVERING THIS PUBLICATION SHALL BE LIABLE FOR ANY DIRECT, INCIDENTAL, CONSEQUENTIAL, INDIRECT, OR PUNITIVE DAMAGES ARISING OUT OF YOUR ACCESS, USE OR INABILITY TO ACCESS OR USE THIS PUBLICATION, OR ANY ERRORS OR OMISSIONS IN ITS CONTENT.

# **Table of Contents**

| 1   | INTRODUCTION                       | 5    |

|-----|------------------------------------|------|

| 1.1 | Product Features                   | 5    |

| 1.2 | System Components                  | 6    |

| 1.3 | Optical Assemblies                 | 8    |

| 1.4 | Evaluation Kit                     | .10  |

| 1.5 | Functional Description             | .11  |

| 1.6 | Management Interface               | .13  |

| 2   | ON- BOARD CONNECTOR SPECIFICATIONS | .14  |

| 2.1 | Drawings and 3D Models             | .14  |

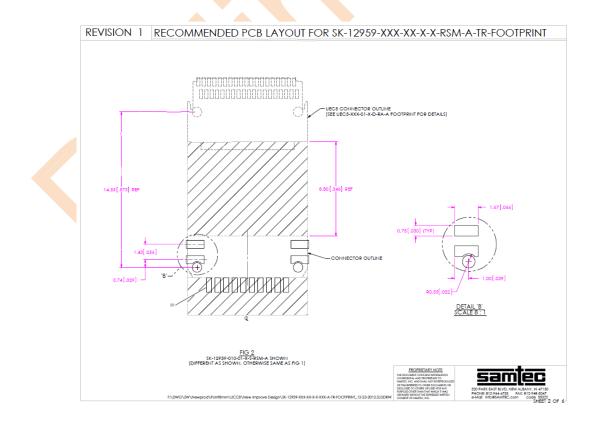

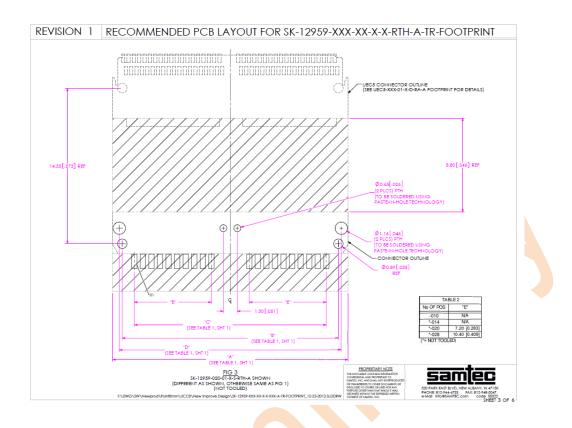

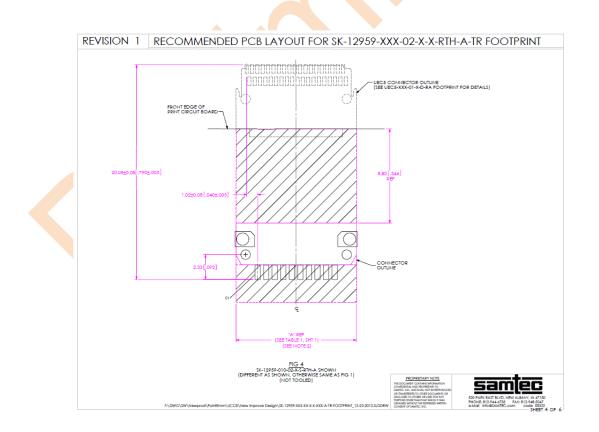

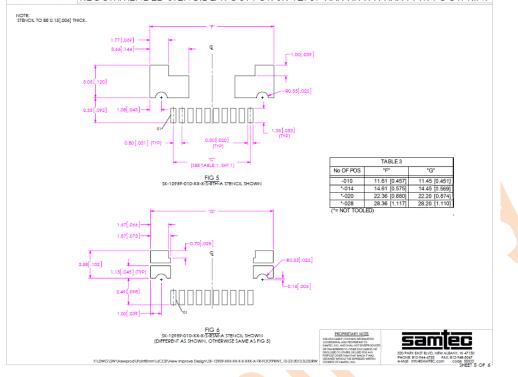

| 2.2 | Connector Footprints               | .14  |

| 2.3 | On-Board Connector Layout          | .20  |

| 2.4 | Performance                        | .21  |

| 2.5 | Electrical                         | .24  |

| 2.6 | Environmental                      | .24  |

| 2.7 | Mechanical                         | .25  |

| 2.8 | Processing Recommendations         |      |

| 2.9 | Additional Resources               |      |

| 3   | OPTICAL ASSEMBLY SPECIFICATIONS    | .26  |

| 3.1 | Power                              | .26  |

| 3.2 | High Speed Performance             | .27  |

| 3.3 | Latency                            | . 31 |

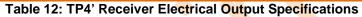

| 3.4 | ECUO- Mechanical                   | . 32 |

| 3.5 | Heat Sinks                         |      |

| 3.6 | Optical Terminations               | . 34 |

| 4   | CONTROL AND MEMORY MAP             |      |

| 4.1 | Control                            | . 39 |

| 4.2 | Memory Map                         |      |

| 5   | POWER MANAGEMENT                   | .83  |

| 5.1 | Receiver                           |      |

| 5.2 | Transmitter                        |      |

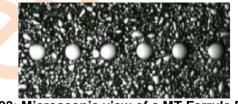

| 6   | ON BOARD CONNECTOR PIN OUT         |      |

| 6.1 | Electrical Connector Pin Outs      |      |

| 6.2 | Transmit                           |      |

| 7   | OPTICAL CONNECTOR PIN OUT          |      |

| 7.1 | ECUO-T12 Optical Connector Pin Out |      |

| 7.2 | ECUO-R12 Optical Connector Pin Out |      |

| 7.3 | ECUO-Y12 Optical Connector         |      |

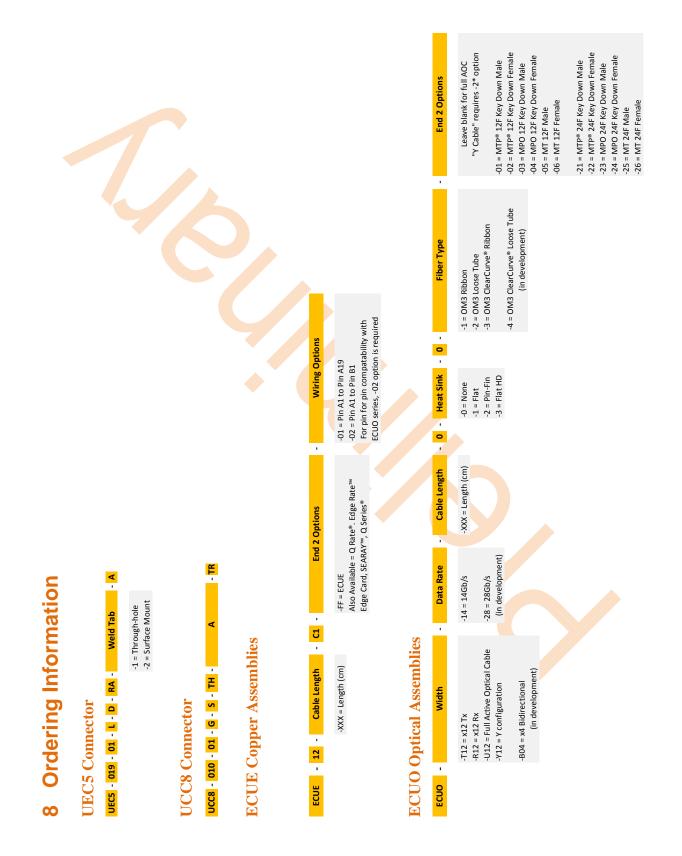

| 8   | ORDERING INFORMATION               |      |

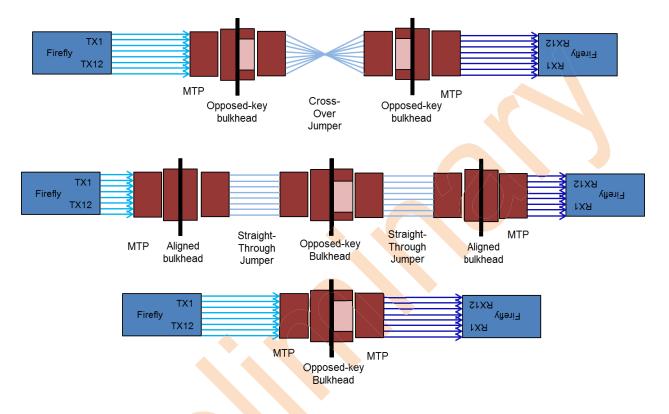

| 9   | FIBER CONNECTIVITY                 | . 92 |

|     |                                    |      |

|     |                                    |      |

|     |                                    |      |

|     |                                    |      |

|     |                                    |      |

# List of Figures

| Figure 1: FireFly™ Application using Copper and Optical Assemblies                                    | 5    |

|-------------------------------------------------------------------------------------------------------|------|

| Figure 2: FireFly™ x12 Connector System                                                               | 6    |

| Figure 3: FireFly™ On Chip Example                                                                    | 6    |

| Figure 4: ECUE 12 Pair Copper Cable                                                                   | 7    |

| Figure 5: Accelerate™ Twinax Ribbon FireFly Assembly                                                  | 7    |

| Figure 6: Close Up View of Accelerate Based Cable End                                                 | 7    |

| Figure 7: Half Cable                                                                                  | 8    |

| Figure 8: Active Optical Cable                                                                        | 8    |

| Figure 9: Y Cable                                                                                     |      |

| Figure 10: Standard Heatsinks                                                                         |      |

| Figure 11: 4 x 3 Multi-Row FireFly™ Arrangement                                                       | 9    |

| Figure 12: FireFly™ Evaluation Kit                                                                    |      |

| Figure 13: ECUO-T12 Block Diagram                                                                     | .11  |

| Figure 14: ECUO-R12 Block Diagram                                                                     | . 12 |

| Figure 15: Breakout Region                                                                            | . 20 |

| Figure 16: UEC5 Model                                                                                 |      |

| Figure 17: Port Numbering Diagram for Simulation                                                      |      |

| Figure 18: Differential Insertion Loss for Ports 1-12                                                 | . 22 |

| Figure 19: Differential Return Loss for Ports 1-12                                                    |      |

| Figure 20: Differential Impedance for Ports 1-12                                                      |      |

| Figure 21: Differential S-parameter Performance                                                       |      |

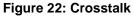

| Figure 22: Crosstalk                                                                                  |      |

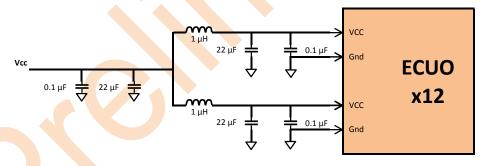

| Figure 23: Recommended Power Filtering Circuit                                                        |      |

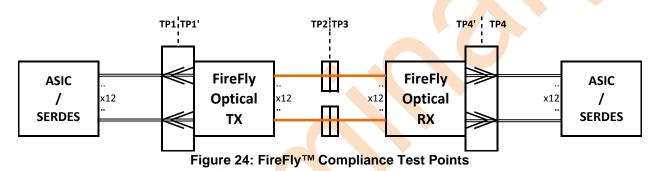

| Figure 24: FireFly™ Compliance Test Points                                                            |      |

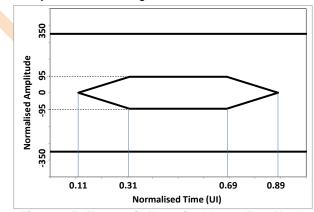

| Figure 25: Transmit Electrical Input Eye Ma <mark>sk</mark>                                           |      |

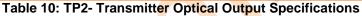

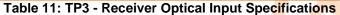

| Figure 26: Transmit Output Optical Eye                                                                |      |

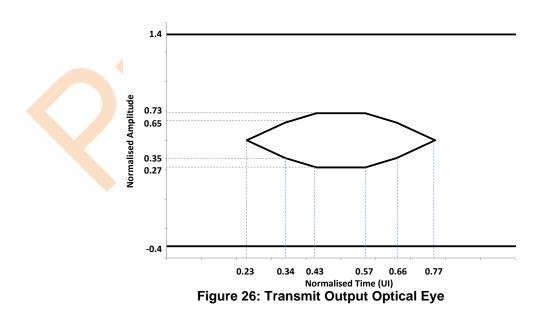

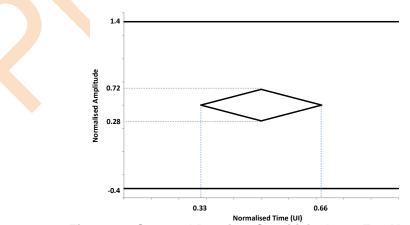

| Figure 27: Stressed Receiver Sensitivity Input Eye Mask                                               |      |

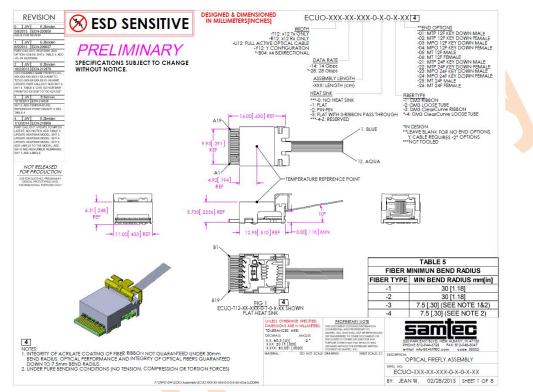

| Figure 28: Microscopic view of a <mark>MT</mark> Ferrule End Face                                     |      |

| Figure 29: 12F and 24F Female MT Ferrule Connectors                                                   |      |

| Figure 30: Male and Female MT Ferrules with Connecting Clip                                           |      |

| Figure 31: MPO Connecto <mark>r</mark>                                                                |      |

| Figure 32: 24F MPO Connector with Keying Feature Highlighted                                          |      |

| Figure 33: Fiber Numberin <mark>g Co</mark> nvention for 12F and 24F Connectors                       |      |

| Figure 3 <mark>4: Exam</mark> pl <mark>e of</mark> an MPO/MTP Adaptor                                 |      |

| Figure 35: MT Prizm Ferrule                                                                           |      |

| Fig <mark>ure</mark> 36: Man <mark>ag</mark> ement interface two wire serial interface timing diagram |      |

| Figu <mark>re 37</mark> : Fire <mark>Fl</mark> y™ x12 Optical Assembly Memory Map                     |      |

| Figure <mark>38: Rec</mark> eiver Output Signal Matrix                                                |      |

| Figure 39: FireFly™ Connector Footprint                                                               |      |

| Figure 40: ECUE-12-XXX-01-01-01-01 Straight Configuration (A1 to A19)                                 |      |

| Figure 41: ECUE-12-XXX-01-01-02-01 Cross Configuration (A1 to B1)                                     |      |

| Figure 42: ECUO Pin Out                                                                               |      |

| Figure 43: Recommended Fiber Link Implementations                                                     | . 92 |

# **Change History**

| Revision # | Reason                  | Author     | Date       |

|------------|-------------------------|------------|------------|

| Draft 01   | Working Draft           | Kevin Burt | 11/25/2013 |

| Draft 02   | Working Draft- Reformat | Kevin Burt | 1/13/2014  |

| Draft 03   | Preliminary Document    | Kevin Burt | 02/02/2014 |

## **1** Introduction

### **1.1** Product Features

The FireFly<sup>™</sup> Micro Flyover System is the first inside the box interconnect system that gives the designer a choice of using either micro footprint optical or copper interconnects to meet today's and future data rate requirements and future proofing the next generation. The FireFly<sup>™</sup> system enables chip-to-chip, board-to-board and system-to-system connectivity at data rates up to 28Gb/s. Current cable versions offer 12 channels of 14Gb/s providing 168Gb/s total bandwidth.

By taking the data connections "off-board" with FireFly<sup>™</sup> fly over cables, the signal integrity design is made significantly easier, and the electrical performance improved. Allowing data to fly over lossy board materials and other signal degrading components negates the need for the layout complexities that are required to design for high speed signalling/

Unlike existing optical engine-based solutions, thermal operating conditions are acknowledged and designed for by including an integral heat sink. The heat sink is available in several default designs to allow for air cooling or with cold plate liquid cooling. In addition, the flexible design accepts customer specific heat sinks for easy integration into existing thermal solutions.

Due to Samtec's extensive catalogue of connector solutions, the copper FireFly<sup>™</sup> assembly is made even more powerful by allowing use of different connector types for the far end. This enables the seamless connection between new boards and existing products without forcing a redesign.

Figure 1: FireFly<sup>™</sup> Application using Copper and Optical Assemblies

### 1.2 System Components

#### **1.2.1 On Board Connector and Transceiver**

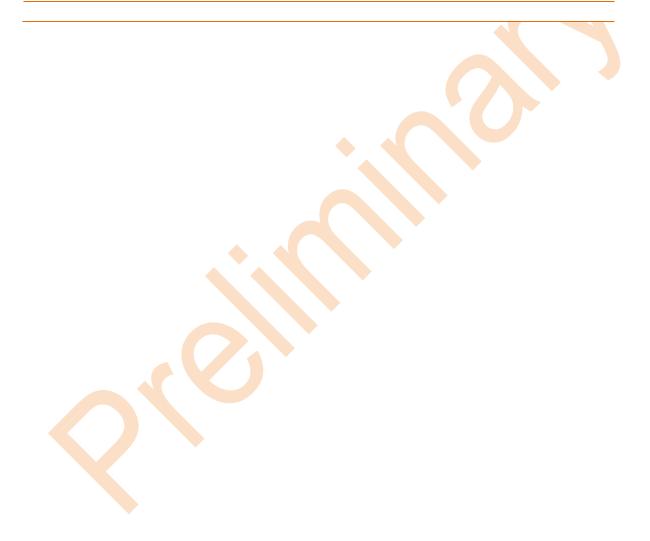

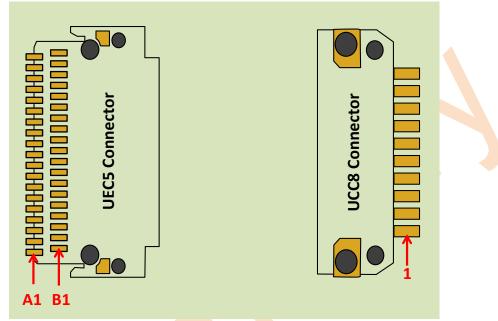

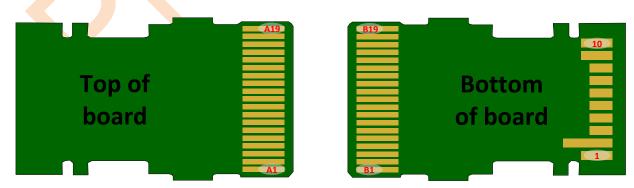

The FireFly<sup>™</sup> Connector system is a two part connector designed for applications up to 28 GB/s. It is based on two connectors, a micro high speed edge connector (UEC5, shown rear left) with two rows of 19 positions providing 12 differential lanes and a 10 position positive latch connector (UCC8, shown front right).

Figure 2: FireFly™ x12 Connector System

The UEC5 connector is used to connect the high speed data signals from the host system to the inputs of the optical or copper FireFly<sup>™</sup> assemblies.

The UCC8 connector provides mechanical support in conjunction with a mechanical latch on the FireFly<sup>™</sup> assembly. In addition, it provides power and low speed communications for optical assemblies.

The on-board connector system is designed for placement on a host board or directly on an IC package. In addition, it enables on-package applications due to the separation of the high speed signals and the power pins.

Figure 3: FireFly<sup>™</sup> On Chip Example

For on package applications, the UEC5 connector is co-packaged with the IC and the UCC8 is placed on the board. Installing the connector onto the IC package enables the shortest possible trace length to maximize performance a high density interconnects. To accommodate the increased height of combined UEC5 connector and substrate, the UCC8 can be configured in different heights.

Detailed Connector specifications can be found in Section 2. On-board connector pin outs can be found in Section 6.1

#### 1.2.2 Copper Cables

FireFly<sup>TM</sup> copper cables are available based on Samtec's 50 $\Omega$  38 AWG, Micro coax ribbon cable. This cable provides performance up to 28 Gb/s on twelve 100  $\Omega$  differential lanes and comes as standard with a FireFly<sup>TM</sup> connector on end two.

Figure 4: ECUE 12 Pair Copper Cable

In addition to the standard connector on the second end of the cable, the assembly can be customised with a wide variety of Samtec connectors. Please contact <u>HDR@samtec.com</u> for further information on cables built with any of the following as the second end:

- Edge Card,

- SEARAU™

- Q Rate®

- Q Series®

- Edge Rate™

For applications which require improved Signal Integrity or a lower profile, Samtec also offers FireFly™ cables based on our 100 Ω 30AWG, Accelerate<sup>™</sup> Twinax Ribbon Cable.

Figure 5: Accelerate<sup>™</sup> Twinax Ribbon FireFly Assembly

This cable will plug into the FireFly<sup>™</sup> connector set, however it will result in a slightly larger keep out area due to the different cable construction and the use of a screw down retention system.

Figure 6: Close Up View of Accelerate Based Cable End

In addition to the lower profile and increased SI performance, the Accelerate<sup>™</sup> based cable can be configured so that sideband signals can be carried via the UCC8 connections. Please contact <u>HDR@samtec.com</u> for further information.

### **1.3 Optical Assemblies**

Optical Assemblies are available in three different configurations.

- Half Cable

- Active Optical Cable

- Y Cable

The same optical engines are used in each cable. As a result, the differences are with the assembly and not the optical engine form factor or performance. All engines are unidirectional, that is there are separate transmit and receive engines each with 12 channels either transmitting or receiving data. Bidirectional assemblies are supported by combining a transmit and receive engine into a single Y cable (see below)

#### **Half Cables**

Figure 7: Half Cable

#### **Active Optical Cables**

Half cables are available with either a transmit or a receive optical engine joined to an optical connector with a 12-fiber optical cable.

These assemblies are customisable to different lengths and with different fiber types, different heat sinks and different optical connectors.

Active optical cables are available with a transmit optical engine on one end and a receive optical engine on the second end.

These assemblies can also be configured to different lengths and with different fiber types, different heat sinks and different optical connectors.

#### Figure 8: Active Optical Cable

#### **Y** Cables

Figure 9: Y Cable

Y *cables* consist of both a transmit optical engine and a receive optical engine connected to a single 24 Fiber optical connector.

Again, these assemblies are customisable to different lengths (identical for transmit and receive) and with different fiber types, different heat sinks and different optical connectors.

#### 1.3.1 Heat Sink Options

FireFly<sup>™</sup> optical assemblies can be configured with a choice of standard heat sinks shown in Figure 10. These heat sink designs support air flow cooling and cold plate cooling. In addition, the FireFly<sup>™</sup> design allows the use of custom heat sinks that allow the integration of cooling solutions for multiple components.

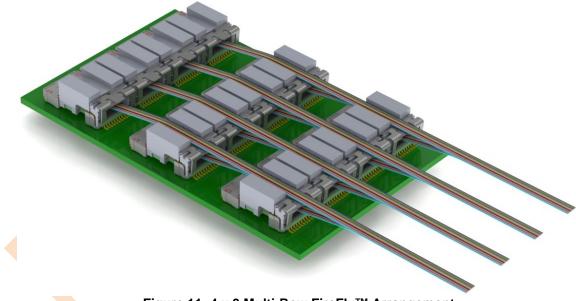

The *flat with 3-ribbon pass-through* heat sink is intended for ultra-high density applications. The angled recess in the heat sink is designed to accommodate the fibers from up to three other ECUO optical assemblies configured in stacked rows. This is shown in Figure 11 (only shown with 3 stacked rows and 2 fibers being passed through for simplicity).

Figure 11: 4 x 3 Multi-Row FireFly™ Arrangement

In addition to the standard heat sinks listed, Samtec will work with customers to create heat sinks optimised for their specific designs<sup>1</sup>. For further information, please contact your local sales representative or <u>firefly@samtec.com</u>.

More information on Heatsinks can be found in Section 3.5.

<sup>&</sup>lt;sup>1</sup> Minimum order quantity or NRE may be required

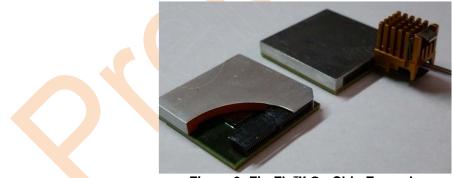

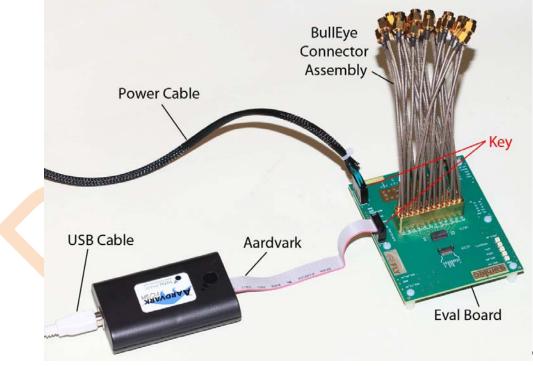

### **1.4** Evaluation Kit

To assist with the evaluation of the FireFly<sup>™</sup> system, Samtec has created an evaluation kit. The FireFly<sup>™</sup> evaluation kit is rated up to 25 Gb/s and is shown in Figure 12.

The FireFly<sup>™</sup> evaluation kit consist of a break-out board connecting a FireFly<sup>™</sup> socket (UEC5 and UCC8 connectors) to a 2x12 Bull's Eye<sup>™</sup> connector landing pads and bringing low speed signals and power rails to various standard connectors.

A mating Samtec Bull's Eye connector with 24 cables terminated with SMA connectors allows for connecting all 12 channels to test equipment. A second Bull's Eye connector landing pad provides standard open and thru circuits to enable de-embedding of the Bull's Eye and PCB affects on the high speed signals.

The kit includes the following items:

- 1 each FireFly<sup>™</sup> PCB break-out board

- 1 each Bull's Eye x24 block and 2x nuts

- 2 each Bull's Eye x12 ground insert

- 24 each Bull's Eye to SMA cable

- 1 each Bull's Eye cable removal tool

- 1 each Aardvark USB to I2C dongle and USB cable

- 1 each USB memory stick with Aardvark driver, FireFly™ Optical Engine client interface, FireFly™ Optical Engine user manual

Figure 12: FireFly™ Evaluation Kit

The part number to purchase the evaluation kit is FIK-FIREFLY-01.

### 1.5 Functional Description

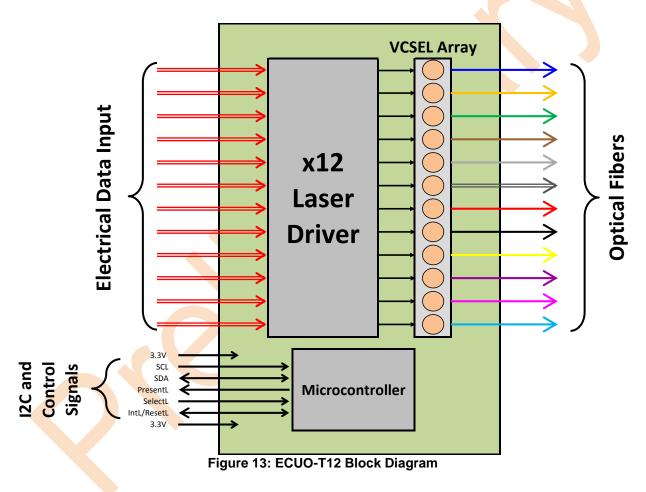

#### 1.5.1 ECUO-T12 Transmitter

The ECUE-T12 optical assembly incorporates a 12-channel VCSEL array, a 12-channel laser driver, diagnostic monitors, control and bias blocks. The transmit input buffer provides CML compatible differential inputs presenting a nominal differential input impedance of 100  $\Omega$ . AC coupling capacitors are located on the optical engine board and therefore are not required on the host board.

An LVTTL compatible Two-Wire Serial (or  $I_2C$ ) interface is provided for module control and diagnostics. Status, alarm and fault information are available via the TWS interface. To reduce the need for polling, a hardware interrupt signal is provided to inform hosts of an assertion of an alarm, and Transmitter (Tx) fault.

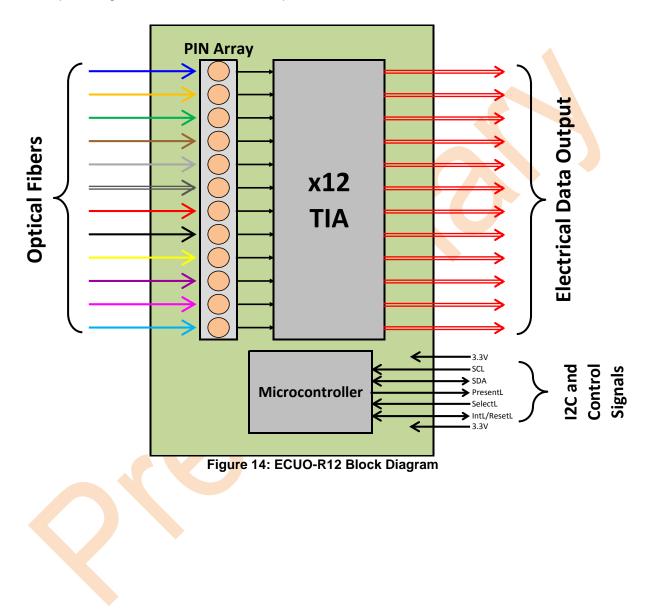

#### 1.5.2 ECUO-R12 Receiver

The ECUE-R12 optical assembly incorporates a 12-channel PIN photodiode array, a 12-channel TIA array, diagnostic monitors, control, and bias blocks. The Receiver Output Buffer provides CML compatible differential outputs for the high speed electrical interface presenting nominal single-ended output impedances of 50  $\Omega$  to AC ground and 100  $\Omega$  differentially. Again, AC coupling capacitors are located on the optical engine and are therefore not required on the host board.

### **1.6** *Management Interface*

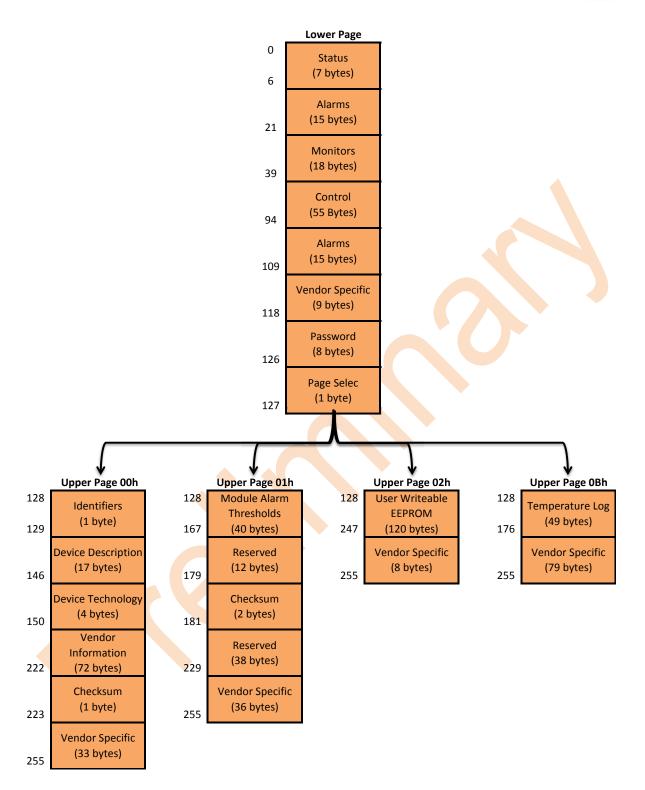

Each optical engine has an I2C based management interface that is based on that defined for the CXP cables in the specification, *Infiniband™ Architecture Specification Volume 2, Release 1.3.* The specified memory map has been:

- Modified to separate Tx and Rx functionality

- Modified to use of Module Select Pin to allow multiple engines on the bus

- Simplified to reflect product features

- Expanded to provide additional features

This management interface provides digital diagnostics and control/monitor functional control to the host system. The on board microcontroller monitors and reports this information via the I2C interface.

The following module and channel digital diagnostic parameters are monitored:

- Temperature

- Supply Voltage

The microcontroller will generate an Interrupt Flag, by pulsing low the IntL signal, when an operational fault occurs. The host can identify the source of the interrupt by reading the appropriate registers through the I2C interface. The following Interrupt Flags are provided:

#### Transmitter

- Tx Fault

- Provided for each channel, indicating that a fault condition relating to that specific laser modulators has occurred

- High Temperature

- Heat sink temperature has exceeded maximum allowed temperature

- Low Temperature

- Heat sink temperature has dropped below minimum allowed temperature

- High Vcc

- o Supply voltage has exceeded maximum allowed voltage

- Low Vcc

- Supply voltage has dropped below allowed voltage

#### Receiver

•

- Rx LOS

- Provided for each channel, indicating that the optical power input into the receiver has dropped below a minimum allowed value

- High Temperature

- 6. Heat sink temperature has exceeded maximum allowed temperature

- Low Temperature

- Heat sink temperature has dropped below minimum allowed temperature

- High Vcc

- Supply voltage has exceeded maximum allowed voltage

- Low Vcc

- Supply voltage has dropped below allowed voltage

More Information on the management interface can be found in Section 0

## **2** On- Board Connector Specifications

### 2.1 Drawings and 3D Models

Three Dimensional models and product prints for the UEC5 and UCC8 connectors showing dimensions, footprint and options will be available at:

http://www.samtec.com/cable-systems/active-optics/on-board-optical/firefly.aspx.

Prior to general release, please contact optics@samtec.com for the most up to date versions.

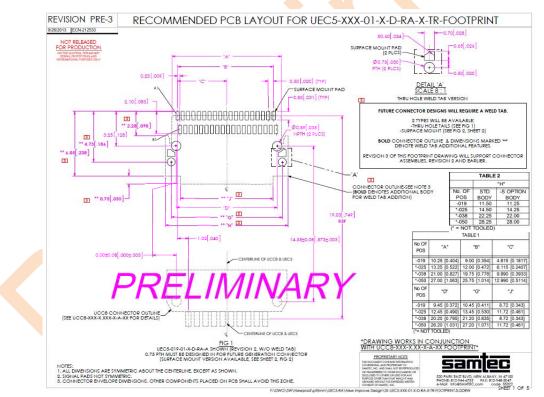

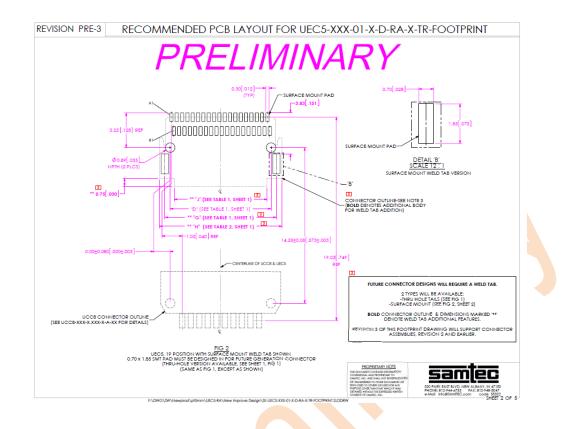

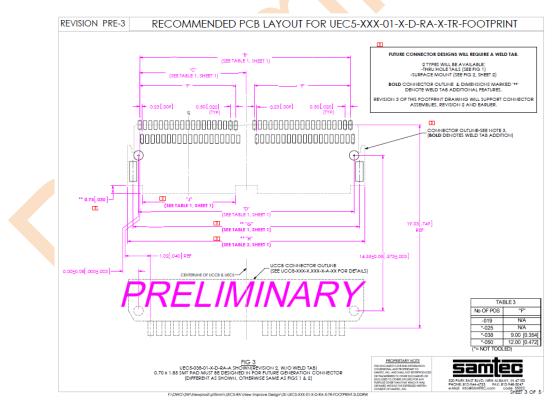

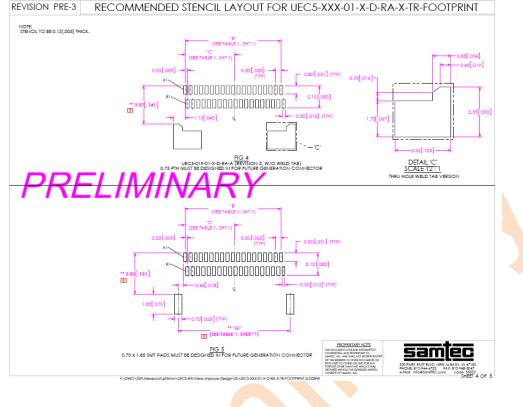

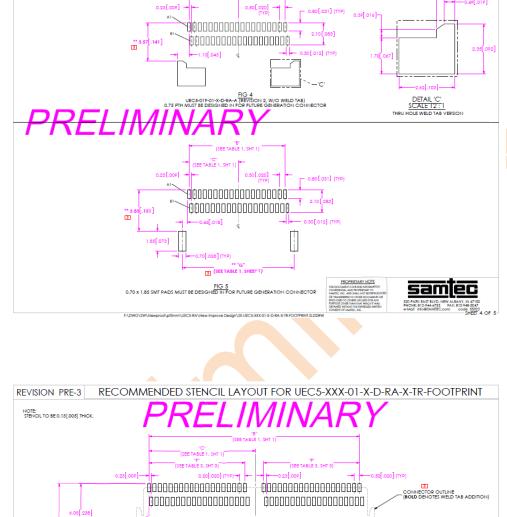

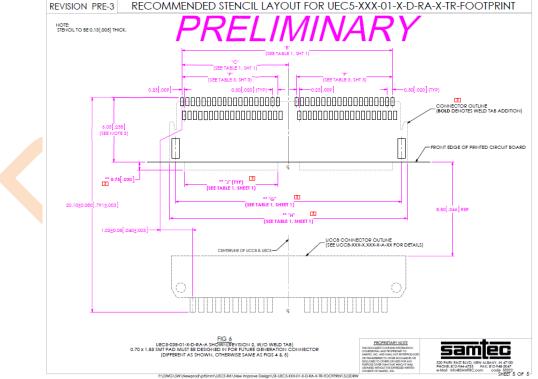

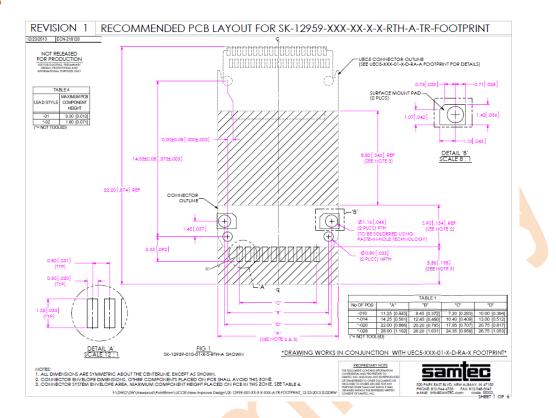

### 2.2 Connector Footprints

Detailed Connector Footprint information is available for the FireFly<sup>™</sup> connectors and will be available at: <u>http://www.samtec.com/technical-specifications/Default.aspx?SeriesMaster=UEC5</u> for the UEC5 and <u>http://www.samtec.com/technical-specifications/Default.aspx?SeriesMaster=UCC8</u> for the UCC8 Prior to general release, please contact <u>optics@samtec.com</u> for the most up to date versions of these files.

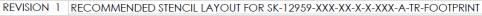

#### UEC5

#### UCC8

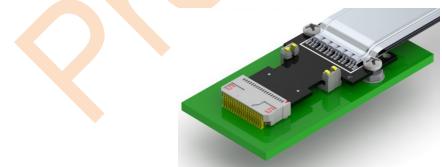

### 2.3 On-Board Connector Layout

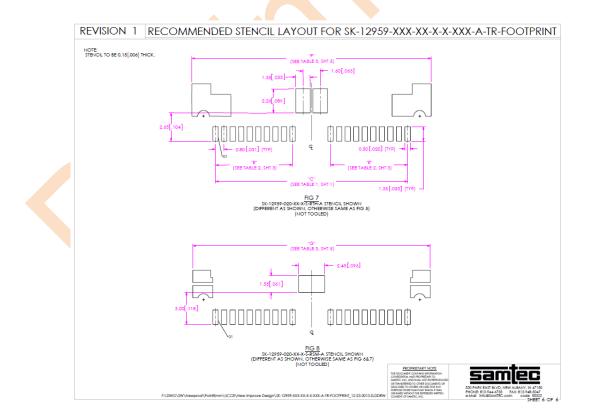

Layout design breakout regions are available for the FireFly<sup>™</sup> connector systems. These are intended to streamline the design process and are available on demand.

Figure 15: Breakout Region

Please contact <u>SIG@samtec.com</u> for further information.

### 2.4 Performance

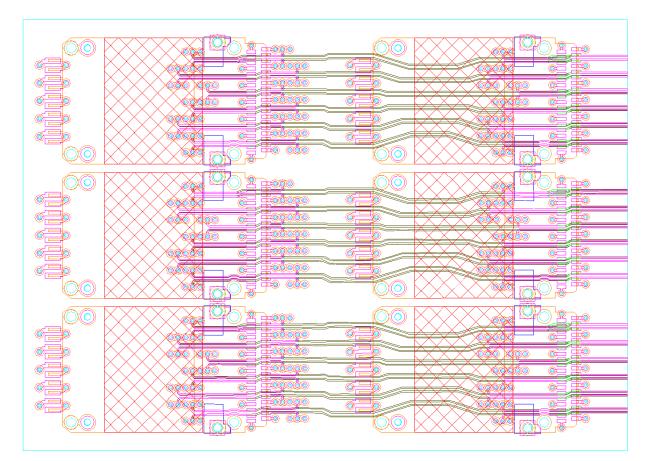

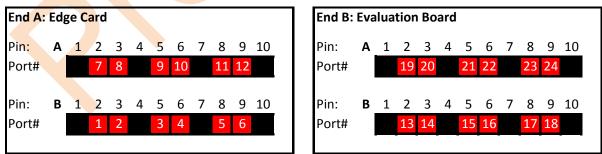

The performance of the UEC5 was investigated using a full wave model of the UEC5 to an edge card as shown in Figure 16. Note, ports are  $50\Omega$  and de-embedding was not used as only a portion of the traces were retained on the test card.

The port numbering for the simulation is shown in Figure 17. Note that Row B corresponds to the longer pins.

Figure 17: Port Numbering Diagram for Simulation

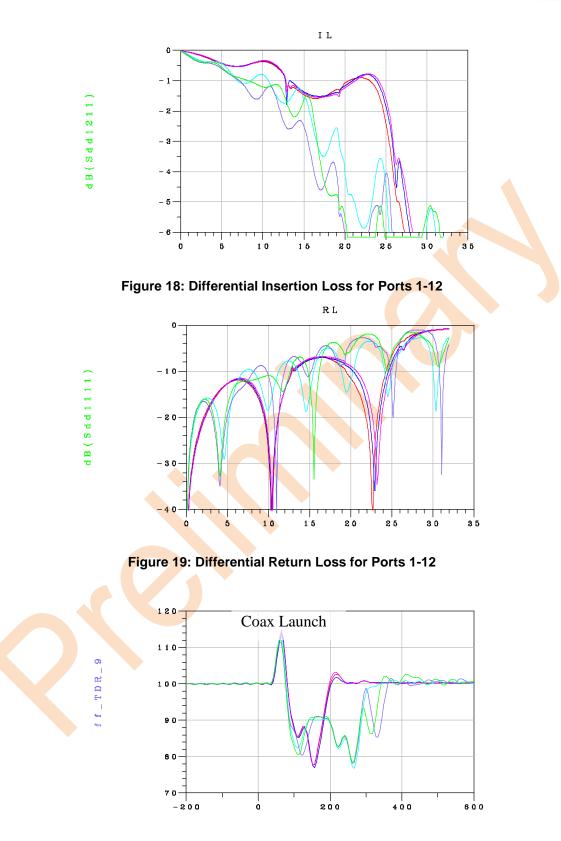

The simulation results are shown in Figure 18, Figure 19 and Figure 20.

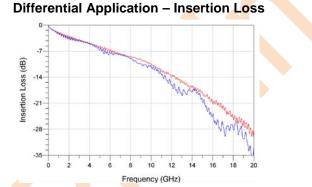

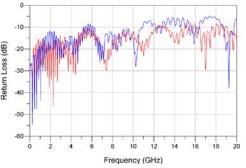

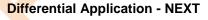

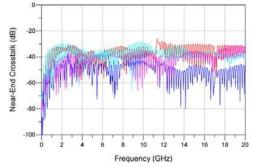

The performance of the UEC5 was characterised by measuring performance of the connector and a FireFly<sup>™</sup> ECUE-12-050-01-01-01 cable (50cm, 38awg micro coax cable). These results are summarised in Table 1, Figure 21 and Figure 22. Further information regarding test methodology and results can be found at: <u>http://www.samtec.com/Documents/WebFiles/testrpt/hsc-report\_ECUE\_web.pdf</u>.

| Parameter             | Units | Min  | Туре | Max | Comments                |

|-----------------------|-------|------|------|-----|-------------------------|

| 3dB Bandwidth         | GHz   |      | 5.5  |     | Single Ended            |

| -7dB Insertion Loss   | GHz   |      | 5.9  |     | Long Row                |

| -70D INSERIOR LOSS    | GHZ   |      | 5.2  |     | Short Row               |

| 10dB Return Loss      | GHz   | 10.9 |      |     | Long Row                |

|                       | GHZ   | 4.5  |      |     | Short Row               |

|                       |       |      |      | -20 | In Row-Long Row         |

| Near End Crosstalk    | dB    |      |      | -20 | In Row-Short Row        |

| Near End Crosslak     | uВ    |      |      | -20 | Xrow                    |

|                       |       |      |      | -20 | Diagonal                |

|                       |       |      |      | -20 | In Row-Long Row         |

| Far End Crosstalk     | GHz   |      |      | -20 | In Row-Short Row        |

| Fai Ellu Clossiaik    | GHZ   |      |      | -20 | Xrow                    |

|                       |       |      |      | -20 | Diagonal                |

| Long/Short Delay Skew | Ps    |      | 12   |     | Includes Cable Assembly |

Table 1: High Speed Performance

Differential Application – Return Loss

**Differential Application - FEXT**

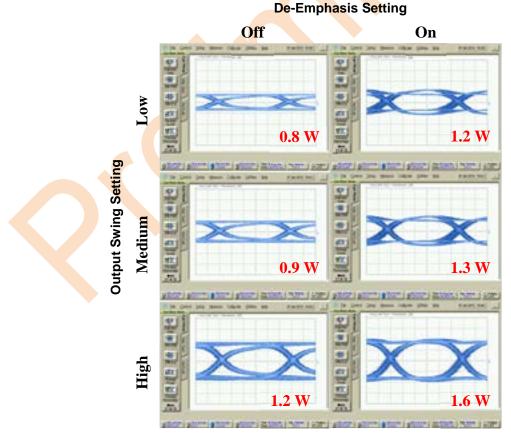

### 2.5 Electrical