# OPERATING MANUAL MODEL 71861

4-channel 200 MHz A/D with DDCs and Kintex UltraScale FPGA Jade Family XMC Module

Pentek, Inc. One Park Way Upper Saddle River, NJ 07458 (201) 818–5900 http://www.pentek.com

Copyright © 2016-2018

Manual Part No: 800.71861

Rev. 1.4 - May 18, 2018

|         | Model 71861 Operating Manual – Revision History |                                                                                                                                                                                                                                                                                  |  |  |  |

|---------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Date    | Revision                                        | Comments                                                                                                                                                                                                                                                                         |  |  |  |

| 12/8/16 | 0.1                                             | Initial publication                                                                                                                                                                                                                                                              |  |  |  |

| 2/8/17  | 0.2                                             | In General Description – Principle of Operation, Memory, and Model 71861<br>Specifications, deleted Option 150 – DDR4 memory is standard.                                                                                                                                        |  |  |  |

| 5/15/17 | 1.0                                             | Updated software description. Register information is only available in the HTML help version of this manual.                                                                                                                                                                    |  |  |  |

| 7/12/17 | 1.1                                             | Added Getting the Model 71861 User Manual Library. Added note to DMA section in Chapter 4. Added memory map addresses for Linked List Descriptor RAM to DMA channels in the Data Acquisition table in Chapter 5.                                                                 |  |  |  |

| 9/19/17 | 1.2                                             | Revised Getting the Model 71861 User Manual Library and Updates to It.                                                                                                                                                                                                           |  |  |  |

| 1/15/18 | 1.3                                             | Added maximum power input and power consumption data to Model<br>71861 Specifications. Revised PMC Connector (Option 104). Revised SW1<br>default configuration in DIP Switch Settings. Revised diagram in Sync Bus.<br>Moved Navigator BSP section into a separate new chapter. |  |  |  |

| 5/18/18 | 1.4                                             | Revised Pre- Trigger Control.                                                                                                                                                                                                                                                    |  |  |  |

#### Warranty

Pentek warrants that all products manufactured by Pentek conform to published Pentek specifications and are free from defects in materials and workmanship for a period of one year from the date of delivery when used under normal operating conditions and within the service conditions for which they were furnished. The obligation of Pentek arising from a warranty claim shall be limited to repairing or at its option, replacing without charge, any product that in Pentek's sole opinion proves to be defective within the scope of the warranty. Pentek must be notified in writing of the defect or nonconformity within the warranty period and the affected product returned to Pentek within thirty days after discovery of such defect or nonconformity. Buyer shall prepay shipping charges, taxes, duties and insurance for products returned to Pentek for warranty service. Pentek shall pay for the return of products to buyer except for products returned from another country.

Pentek shall have no responsibility for any defect or damage caused by improper installation, unauthorized modification, misuse, neglect, inadequate maintenance, or accident, or for any product that has been repaired or altered by anyone other than Pentek or its authorized representatives.

The warranty described above is buyer's sole and exclusive remedy and no other warranty, whether written or oral, is expressed or implied. Pentek specifically disclaims fitness for a particular purpose. Under no circumstances shall Pentek be liable for any direct, indirect, special, incidental, or consequential damages, expenses, losses or delays (including loss of profits) based on contract, tort, or any other legal theory.

#### **Copyrights**

The contents of this publication are Copyright ©2016–2018, Pentek, Inc. All Rights Reserved. Contents of this publication may not be reproduced in any form without written permission.

#### **Trademarks**

Pentek, Jade, and Navigator are trademarks or registered trademarks of Pentek, Inc.

Linux is a registered trademark of Linus B. Torvalds. Microsoft and Windows are registered trademarks of Microsoft Corporation. PCI, PCI Express, PCIe, and PCI–SIG are trademarks or registered trademarks of PCI–SIG. Xilinx, Kintex, UltraScale, and Vivado are registered trademarks or trademarks of Xilinx, Inc.

# Table of Contents

| Table of Contents                                             |    |

|---------------------------------------------------------------|----|

| Chapter 1: Introduction                                       |    |

| General Description                                           |    |

| Features                                                      |    |

| Model 71861 Block Diagram                                     |    |

| Principle of Operation                                        |    |

| Analog to Digital Input Conversion                            |    |

| A/D Acquisition                                               | 11 |

| Digital Downconversion                                        | 11 |

| Clocking and Synchronization                                  | 11 |

| Xilinx Kintex UltraScale FPGA                                 |    |

| Memory                                                        |    |

| PCI Express Interface                                         |    |

| XMC Interface                                                 |    |

| Board Support Software: Navigator Design Suite                |    |

| Navigator Board Support Package (BSP)                         | 13 |

| Navigator FPGA Design Kit (FDK)                               |    |

| Getting the Model 71861 User Manual Library and Updates to It |    |

| Instructions for Windows                                      | 15 |

| Instructions for Linux                                        | 16 |

| Supporting Documentation                                      |    |

| Vendor Datasheets and User Guides                             |    |

| Pentek IP Core User Guides                                    |    |

| Model 71861 Specifications                                    |    |

| Chapter 2: Installation and Connections                       |    |

| Inspection                                                    | 23 |

| DIP Switch Settings                                           |    |

| PCB LEDs                                                      |    |

| Baseboard Connectors                          |    |

|-----------------------------------------------|----|

| XMC Connectors                                |    |

| PMC Connector (Option 104)                    |    |

| JTAG Connector                                |    |

| Battery Installation                          |    |

| Installing the XMC Module on an XMC Baseboard |    |

| Installation Instructions                     |    |

| Front Panel Connections                       |    |

| Clock Input Connector                         |    |

| Trigger Input Connector                       |    |

| Analog Signal Input Connectors                |    |

| Sync Bus Connector                            |    |

| Front Panel LEDs                              |    |

| Link LED                                      |    |

| User LED                                      |    |

| Master LED                                    |    |

| PPS LED                                       |    |

| Over Temperature LED                          |    |

| Clock LED                                     |    |

| ADC Overload LEDs                             |    |

| Chapter 3: Hardware Resource Operation        |    |

| Overview                                      |    |

| Analog to Digital Input                       |    |

| Timing and Synchronization                    |    |

| Clocks                                        |    |

| Sync Bus                                      |    |

| Interrupt Operation                           | 41 |

| FPGA System Monitor                           |    |

| I2C Bus Controllers                           |    |

| I2C Bus 0                                    |

|----------------------------------------------|

| Main PCB M95234 Temperature Sensor44         |

| Front Panel Module LM83 Temperature Sensor45 |

| Main PCB LTC2990 Voltage Monitor             |

| Si571 Programmable VCXO                      |

| Si5341B AnyRate Clock Generator              |

| I2C Bus 1                                    |

| RAM Memory Operation                         |

| FLASH Memory Operation                       |

| Chapter 4: FPGA IP Core Operation            |

| Overview                                     |

| Channel Nomenclature                         |

| Data I/O Interfaces                          |

| ADC Interface                                |

| Sync Bus Interface                           |

| Timestamp Generate                           |

| ADC AXI4-Stream Merge                        |

| Test Signal Generate                         |

| Data Source Select                           |

| CDCM7005 Control & Clock Generation55        |

| Data I/O Interrupts55                        |

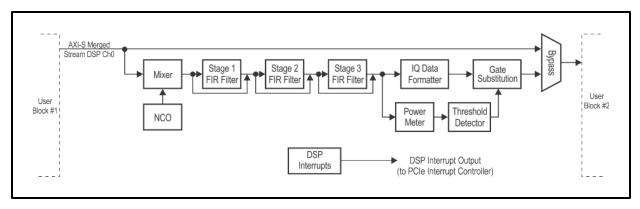

| Digital Signal Processing                    |

| NCO                                          |

| Mixer                                        |

| Stage 1 FIR Filter                           |

| Stage 2 FIR Filter                           |

| Stage 3 FIR Filter                           |

| IQ Data Formatter                            |

| Power Meter                                  |

| Threshold Detector                            |    |

|-----------------------------------------------|----|

| DSP Gate Substitution                         | 57 |

| DSP Bypass Mux                                |    |

| DSP Interrupts                                |    |

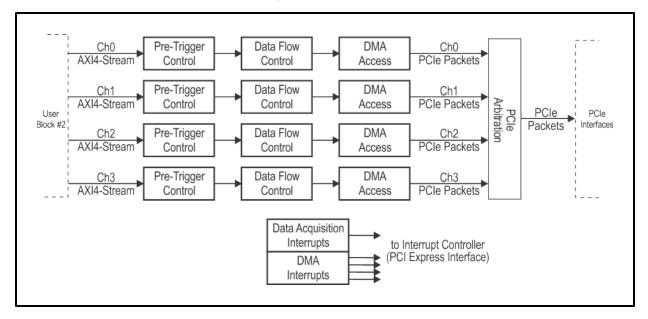

| Data Acquisition                              |    |

| Pre-Trigger Control                           |    |

| Data Flow Control                             | 60 |

| DMA                                           | 60 |

| Data Acquisition Interrupts                   | 61 |

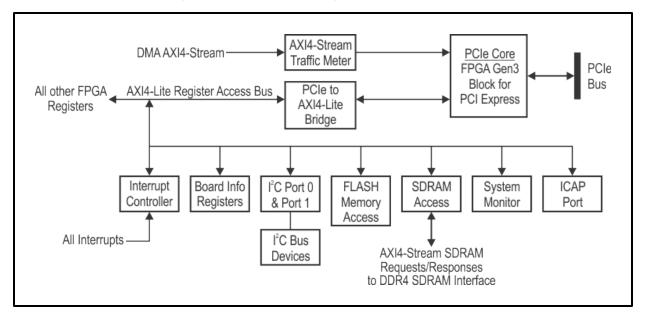

| PCIe Interfaces                               |    |

| AXI4-Stream Traffic Meter                     |    |

| FPGA Gen3 PCIe Core                           | 62 |

| PCIe To AXI4-Lite Bridge                      | 62 |

| Interrupt Controller                          | 63 |

| Board Information Registers                   | 63 |

| I2C Port 0                                    | 64 |

| I2C Port 1                                    | 64 |

| Configuration Flash Access                    | 64 |

| DDR4 SDRAM Access                             | 64 |

| System Monitor                                | 64 |

| ICAP Port                                     | 65 |

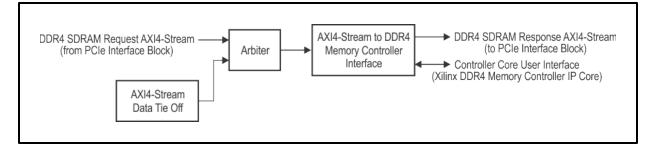

| DDR4 SDRAM Interface                          |    |

| DDR4 Memory Controller Interface              |    |

| AXI4-Stream Data Tie Off                      | 66 |

| User Blocks                                   | 67 |

| Chapter 5: Navigator Board Support Package    | 68 |

| IP Block / Hardware Layer                     |    |

| Board-Specific / PCIe Support / Utility Layer | 69 |

| High Level API Layer                          | 69 |

| Application Layer                  |    |

|------------------------------------|----|

| Chapter 6: Model 71861 Memory Maps | 70 |

| Overview                           | 70 |

| Default FPGA Memory Map            | 71 |

| PCI Express Interfaces             | 71 |

| Data Acquisition                   | 72 |

| Data I/O Interfaces                |    |

| Digital Signal Processing          | 74 |

| User Block Address Space           | 77 |

| PCI Configuration Space Registers  |    |

# **Chapter 1: Introduction**

## **General Description**

Pentek's Jade<sup>™</sup> family Model 71861 is a multichannel, high-speed data converter. The 71861 includes four A/D converters, programmable Digital Downconverters (DDCs), and a large DDR4 memory. In addition to supporting PCI Express Gen 3 as a native interface, the Model 71861 includes optional high-bandwidth connections to the Kintex UltraScale FPGA for custom digital I/O.

The Model 71861 XMC can be attached directly to any digital signal processing (DSP) baseboard equipped with an XMC expansion site, or to an XMC carrier/adaptor, such as the Pentek Model 7807 XMC PCI Express carrier.

This 71861 Operating Manual applies to all of Pentek's Jade family products that include Pentek's Model 71861 XMC, such as the Model 78861 PCIe board, the Model 52861 VPX board, and others.

For access to detailed documentation of the IP Core modules and their programmable registers, refer to the HTML help version of this user manual. You can obtain the HTML version by downloading the User Manual Library for the specific board you are using. Instructions are provided in Getting the Model 71861 User Manual Library and Updates to It.

### Features

- Four 200–MHz 16–bit A/D converters

- Xilinx® Kintex® UltraScale<sup>™</sup> FPGA (Field-Programmable Gate Array)

- Four multiband DDC (digital downconverter) IP Core

- Five gigabytes of DDR4 (Double Data Rate 4th Generation) SDRAM

- Clock synthesizer with programmable clock rates

- LVPECL (Low-Voltage Positive Emitter-Coupled Logic) clock/sync bus for multiboard synchronization

- PCI Express (Gen 1, 2, or 3) interface up to x8 wide

- VITA 42.0 XMC compatible with switched fabric interfaces

- Optional user-configurable gigabit serial interface to the Kintex FPGA

- Optional LVDS (Low-Voltage Differential Signaling) connections to the Kintex FPGA

- Ruggedized and conduction cooled versions available

# Model 71861 Block Diagram

IN 4 (9) IN 1 (q) IN 2 Ŷ IN 3  $(\mathbf{\hat{q}})$ RF In RF In RF In RF In TTL Sync/PPS TTL Gate/Trig RF RF RF RF XFORMER XFORMER XFORMER XFORMER Clk Gate Sync A/D Timing Bus 200 MHz 200 MHz 200 MHz 200 MHz Clock/Sync/ PPS/Gate 16-BIT A/D 16-BIT A/D 16-BIT A/D 16-BIT A/D TIMING Sample Clk / Reference Clk In CONTROL 16 -16 16 ´16 Trigger/Gate In() KINTEX FPGA VCXO 16 780 x8 <sup>-</sup>48 x4 x4 DDR4 FLASH SDRAM 1 Gb PCle FPGA Gigibit 5 GB GPIO Serial I/O Gen3 PMC Baseboard/Carrier Connections ----XMC P15 PMC P14 XMC P16 (Option 104) (Option 105)

Below is a simplified block diagram of the Model 71861 XMC.

# Principle of Operation

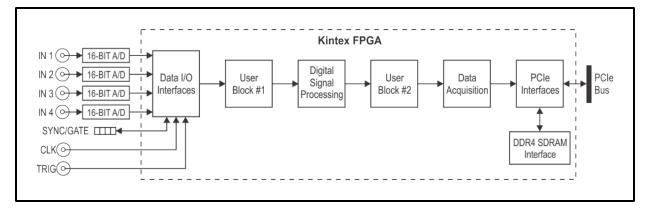

Model 71861 is an A/D module suitable for direct connection to HF or IF ports of a communications or radar system. Using the XMC format, it includes four 200–MHz A/D converters, four digital downconverters, and a Xilinx Kintex UltraScale FPGA.

The 71861 features a Xilinx Kintex UltraScale FPGA for signal interfaces and processing. The FPGA is pre-configured by Pentek to provide signal acquisition buffering functions. This FPGA also provides board interfaces including PCIe and XMC. Custom general purpose I/O connections are provided to the FPGA through the optional PMC P14 connector (Option 104). Custom gigabit serial interfaces may be implemented through the optional XMC P16 connector (Option 105).

Four 200–MHz, 16–bit A/D converters provide data to the FPGA, where the data can be formatted, processed, or routed to board resources, including four multiband digital down-converters.

Model 71861 includes an onboard voltage-controlled crystal oscillator (VCXO) and a programmable clock synthesizer for clocking, but can also accept external clocks through front panel connectors. Model 71861 is equipped with an front panel sync bus that allows synchronizing A/D processing on multiple boards.

Model 71861 includes five gigabytes of DDR4 SDRAM. This memory is controlled by the FPGA and is available as a memory resource for custom FPGA applications.

Model 71861 is compatible with VITA 42 XMC carrier boards. This standard provides separate serial data links between the XMC and the carrier. These links support Serial RapidIO, PCI Express, and Aurora protocols and provide a dedicated high-speed streaming data path.

Each member of the Jade family is delivered with factory-installed applications ideally matched to the board's analog interfaces, including IP modules for ADC acquisition and digital signal processing, a controller for all data clocking and synchronization functions, a test signal generator, and a PCIe interface.

For applications that require specialized functions, users can install their own custom IP for data processing. Pentek Navigator FPGA Design Kits include all of the factory installed modules as documented source code. Developers can integrate their own IP with the Pentek factory-installed functions or use the Navigator Design Kit to completely replace the Pentek IP with their own.

# Analog to Digital Input Conversion

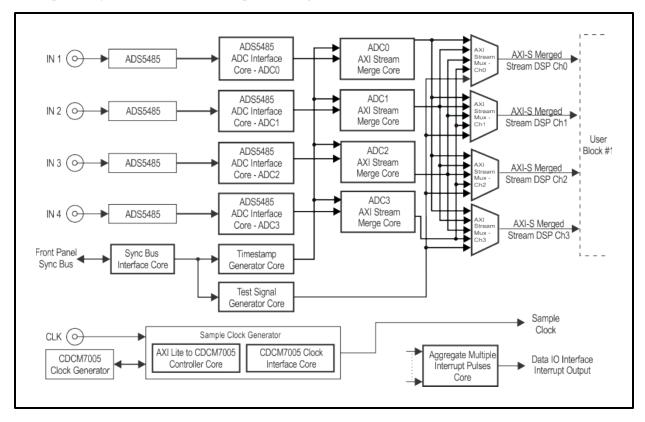

The 71861 front end accepts four full-scale analog HF or IF inputs on front panel SSMC connectors with transformer coupling into four Texas Instruments ADS5485 200–MHz, 16–bit A/D converters (ADCs). The ADC digital outputs are delivered into the Kintex UltraScale FPGA for signal processing by the ADC Acquisition Modules and the Digital Downconverters.

# A/D Acquisition

The 71861 features four blocks of A/D Acquisition IP Core modules for capturing and moving data. Each block of IP modules can receive data from any of the four A/Ds or from a test signal generator.

Each block of IP modules includes a DMA IP module for easily moving A/D data through the PCIe interface. Each powerful linked-list DMA module is capable of a unique Acquisition Gate Driven mode. In this mode, the length of a transfer performed by a link definition need not be known prior to data acquisition; rather, it is governed by the length of the acquisition gate. This is extremely useful in applications where an external gate drives acquisition and the exact length of that gate is not known or is likely to vary.

For each transfer, the DMA module can automatically construct metadata packets containing A/D channel ID, a sample–accurate time stamp and data length information. These actions simplify the host processor's job of identifying and executing on the data.

## **Digital Downconversion**

The 71861 provides four DDC IP Core channels. Because of the flexible input routing of A/D Acquisition, many different configurations can be achieved including one A/D driving all four DDCs or each of the four A/Ds driving its own DDC.

Each DDC has an independent 32-bit tuning frequency setting that ranges from DC to *fs*, where *fs* is the A/D sampling frequency. Each DDC can have its own unique decimation setting, supporting as many as four different output bandwidths for the board. Decimations can be programmed from 2 to 32,768 providing a wide range to satisfy most applications.

The decimating filter for each DDC accepts a unique set of user–supplied 24–bit coefficients. The 80% default filters deliver an output bandwidth of 0.8\*fs/N, where N is the decimation setting. The rejection of adjacent–band components within the 80% output bandwidth is better than 100 dB. Each DDC delivers a complex output stream consisting of 24–bit I + 24–bit Q or16–bit I + 16–bit Q samples at a rate of fs/N.

# **Clocking and Synchronization**

An internal timing bus provides all timing and synchronization required by the A/D converters. It includes clock, sync, and gate or trigger signals. An on-board clock generator receives an external sample clock from a front panel SSMC connector. This clock can be used directly by the A/D or divided by a built-in clock synthesizer circuit. Alternatively, the sample clock can be sourced from an on-board programmable voltage-controlled crystal oscillator. In this mode, the front panel SSMC connector can be used to provide a 10-MHz reference clock for synchronizing the internal oscillator.

A front panel 26-pin LVPECL Clock/Sync connector allows multiple boards to be synchronized. In the slave mode, it accepts inputs that drive the clock, sync and gate signals. In the master mode, it can drive the timing signals for synchronizing multiple boards. Multiple boards can be driven from the bus master, supporting synchronous sampling and sync functions across all connected boards.

# Xilinx Kintex UltraScale FPGA

The Kintex UltraScale FPGA site can be populated with a range of FPGAs to match the specific requirements of the processing task, spanning the KU035 through KU115. The KU115 features 5520 DSP48E2 slices and is ideal for modulation/demodulation, encoding/decoding, encryption/decryption, and channelization of the signals between transmission and reception. For applications not requiring large DSP resources or logic, a lower-cost FPGA can be installed.

Option 104 installs the P14 PMC connector with 24 pairs of LVDS connections to the FPGA for custom I/O. Option 105 installs the P16 XMC connector with dual x4 gigabit links to the FPGA to support serial protocols.

### Memory

The 71861 architecture supports a 5–GB bank of DDR4 SDRAM memory. Custom user--installed functions within the FPGA can take advantage of the memory for many purposes. A 1–gigabit FLASH memory supports booting and FPGA configuration.

### **PCI Express Interface**

The Model 71861 includes an industry-standard interface fully compliant with PCI Express Gen. 1, 2, and 3 bus specifications. Supporting PCIe links up to x8, the interface includes multiple DMA controllers for efficient transfers to and from the baseboard or carrier.

### XMC Interface

The Model 71861 complies with the VITA 42.0 XMC specification. Two connectors each provide dual x4 links or a single x8 link with up to 10 Gb/sec per lane. With dual XMC connectors, the 71861 supports x8 PCIe on the first XMC connector leaving the second connector free to support user–installed transfer protocols specific to the application.

# Board Support Software: Navigator Design Suite

Pentek's Navigator Design Suite includes the Navigator Board Support Package for creating host applications and the Navigator FPGA Design Kit for integrating custom IP into Pentek's factory-shipped design. These two components of the Suite are described below.

### Navigator Board Support Package (BSP)

The Navigator BSP contains software support for Jade boards. This includes a device driver, the Navigator BSP Board Support Library data structures and routines, and example programs. The Navigator BSP enables operational control of the hardware and the IP functions in the FPGA.

The BSP allows software developers to work at a higher level, abstracting many of the details of the hardware through an API. The API allows developers to focus on the task of creating the application by letting the API, the hardware, and the IP-control libraries below it to handle many of the board-specific functions. For developers who want full access to the entire BSP library, complete C-language source code is available.

New applications can be developed on their own or by building on one of the included example programs. All Jade boards are shipped with a full suite of built-in functions, allowing operation without the need for any custom IP development.

The Navigator BSP User's Guide describes how to install and use the BSP software.

The *API Reference Guide for the Navigator BSP* describes the source and include files in the BSP and is available in both HTML and PDF format (**API\_Reference.html** and **API\_Reference.pdf**). The *API Reference Guide* is available in the following location:

Windows: C:\Pentek\BSP\BSP\_X.Y\docs (where X.Y is the version number) or %NAVBSP%\docs

# Linux: /home/username/Pentek/BSP/BSP\_X.Y/docs (where X.Y is the version number) or \$NAVBSP/docs

The *Navigator BSP API Reference Guide* describes the BSP header and source files. These manuals are available in PDF format. The *API Reference Guide* is also available in HTML format.

### Navigator FPGA Design Kit (FDK)

The Navigator FDK was designed to be used with the Xilinx Vivado Design Suite. Vivado includes the IP Integrator design environment. Built around a graphical block diagram interface, the IP Integrator allows developers to leverage existing IP by importing it into their block diagram design. The Navigator FDK provides the complete IP for a specific Jade board. When the design is opened in Vivado's IP Integrator, the developer can access every component of the Pentek design, replacing or modifying blocks as needed for an application.

The Navigator FDK is a very specialized software package intended for users with experience in FPGA logic programming. This package may not be required if the default functions included in the FPGA code, as written by Pentek, satisfy the requirements of your application. The Navigator Board Support Package (BSP) is always required and should be installed before the Navigator FDK. The *Navigator FDK User's Guide* describes how to install and use the FDK software. In addition, an *IP Core Manual* is provided for each IP core in the FDK. These can be accessed via the Vivado IP Integrator. Several tutorials also are available:

- *IP Core Conventions Guide and Example Labs* (807.48111)

- Designing with the PDTI Type AXI-Stream Bus (807.48112)

- Designing with the Navigator DDR4 SDRAM Access Interface (807.48113)

You can get the Navigator FDK and user manuals by contacting <u>sales@pentek.com</u>.

# Getting the Model 71861 User Manual Library and Updates to It

A set of user manuals for Model 71861 is provided in HTML help format. This documentation is provided on a DVD and shipped with the board. When the user manuals are updated, you will be notified. You can get the latest user manual library for your product by following the instructions provided below.

If you have any questions please <u>contact your local representative</u> or Pentek directly:

Mario Schiavone, Sales Director, Pentek, Inc. Phone: +1 (201) 818–5900; Email: sales@pentek.com

To get the user manual library for Model 71861, follow the procedure for the operating system you're using:

#### **Instructions for Windows**

- If your system does not have a recent version of file compression software installed (such as WinZip<sup>™</sup>), you must install it in order to be able to unlock the zip file containing the user manual library. Older file compression utilities may not be able to unlock the zip file. You can obtain free file compression software from 7–Zip at <a href="http://www.7-zip.or-g/download.html">http://www.7-zip.or-g/download.html</a>.

- 2. Click on <u>this link</u> to download the self-extracting zip file for the <u>Model 71861 XMC module user manual library</u>. The file name is <u>71861\_docs.exe</u>.

The zip file for the user manual library is large so downloading it may take a few minutes.

- 3. Put the **71861\_docs.exe** file in the location (folder) in which you want to unzip (extract) the files and double-click **71861\_docs.exe**.

- 4. The zip file is password protected, so you will be prompted to enter the password, which is **71861PEN**.

- 5. A folder named **71861** is extracted. In this folder you'll see several folders (Content, Data, etc.) and several files, including **71861\_docs.htm**.

- 6. To open the user manual library (HTML help), double-click this file: **71861\_docs.htm**. Your browser will display the online help welcome page that provides access to all the user documentation for your board.

The online help welcome page should display a table of contents panel on the left. If that panel is not shown on the left, make your browser window wider. Or reduce the text size using CTRL – (minus).

### **Instructions for Linux**

A self-extracting archive is not available for the Linux platform. The encrypted archive should be extracted using the POSIX port of the 7-zip utility, called **p7zip**. The standard 'unzip' utility in Linux does not support the AES-256 encryption used to password-protect this archive. Binaries (x86, 32-bit) and source code for p7zip are available here: <u>http://sourceforge.net/projects/p7zip/files/</u>. The program is also available as a package in most major Linux distributions and may already be installed on the system.

1. Click on <u>this link</u> to download the zip file for the <u>Model 71861 XMC module user</u> <u>manual library</u>. The file name is <u>71861\_docs.zip</u>.

The zip file for the user manual library is large so downloading it may take a few minutes.

- 2. Put the **71861\_docs.zip** file in the location (folder) in which you want to unzip (extract) the files.

- 3. Execute the following command on the console to extract the files: 7z x 71861\_docs.zip

- 4. The zip file is password protected, so you will be prompted to enter the password, which is **71861PEN**.

- 5. Refer to steps 5 and 6 in the Windows procedure, above.

# Supporting Documentation

### Vendor Datasheets and User Guides

In addition to the operating instructions provided in this manual, you can refer to manufacturer datasheets for the programmable devices on the Model 71861:

- Texas Instruments Inc., ADS5485 Analog-to-Digital Converter Datasheet

- Texas Instruments Inc., LM95234 Temperature Sensor Datasheet

- Texas Instruments Inc., LM83 Temperature Sensor Datasheet

- Silicon Labs, Inc., Si571 Any-Rate VCXO Datasheet

- Texas Instruments, Inc., CDCM7005 Clock Synthesizer Datasheet

- Linear Technology Corp., LTC2990 Quad I2C Voltage, Current, and Temperature Monitor Datasheet

- Silicon Labs, Inc., Si5341 Clock Generator Datasheet

- Xilinx Inc., Kintex UltraScale FPGA System Monitor Users Guide

The documents listed above can be accessed from the HTML version of this manual. Pentek provides these datasheets and user guides for your convenience. However, they might be updated by the manufacturer after we obtain them. The latest version of a product's documentation can be found on the manufacturer's website.

### Pentek IP Core User Guides

Links to Pentek's IP Core User Guides (PDF format) are provided in the HTML version of the user documentation. The Navigator FPGA Design Kit software also links to Pentek's IP Core User Guides.

### Model 71861 Specifications

#### **Analog Signal Inputs**

Connectors: Four front panel SSMC connectors: IN 1, IN 2, IN 3, & IN 4 Input Type: Single-ended, non-inverting Full Scale Input: +8 dBm Maximum Power Input: 14 dBm Coupling: Transformer coupled Input Impedance: 50 ohms Analog Input Transformers: 3dB Passband: 300 kHz to 700 MHz Insertion Loss: 0.58 dB max.

#### Analog to Digital Converters

Quantity: Four Texas Instruments ADS5485 A/D converters Sampling Rate: 10–200 MHz Resolution: 16 bits Clock Source: Selectable from onboard VCXO, front panel SSMC clock, or Sync Bus LVPECL clock input

#### Digital Downconverters (four separate channels)

Decimation Range: 2 to 32,768 in three stages of 2 to 32 LO Tuning Freq. Resolution: 32 bits, 0 to *f*s LO SFDR: >120 dB Phase Offset Resolution: 32 bits, 0 to 360 degrees FIR Filter: 24-bit coefficients (user-programmable) 24-bit output Default Filter Set: 80% bandwidth <0.3 dB passband ripple >100 dB stopband attenuation

#### Sync Bus Inputs/Outputs

Connector Type: Front panel 26-pin connector, SYNC/GATE Signals: CLK In/Out: 2 pins (LVPECL pair) GATE In/Out: 2 pins (LVPECL pair) SYNC In/Out: 2 pins (LVPECL pair) LVTTL GATE/TRIG In: 1 pin (single-ended) LVTTL SYNC/PPS In: 1 pin (single-ended) Spares: 6 pins (3 LVPECL pairs) Grounds: 12 pins Bus Master/Slave: Bus master or bus slave mode selectable via software

**Bus Termination:** Bus termination provided by in-line cable end terminator **Number of Boards Supported:** Up to four boards can be synchronized with a ribbon cable. Systems requiring more synchronized channels can be supported with the Model 7893 Clock Synthesizer.

### <u>Clock</u>

**Clock Source:** Selectable from external or internal clock External: Front panel SSMC CLK, or Sync Bus LVPECL CLK Internal: Generated from programmable VCXO

#### External Clock Input

Connector Type: Front panel SSMC connector, CLK Signal Type: Sine wave Frequency Range: 10 to 800 MHz divider input clock or PLL system reference (when greater than 200 MHz, the input clock must be divided down by the CDCM7005 for the ADC clock) Voltage Range: +0 to +10 dBm Coupling: AC coupled Input Impedance: 50 ohms

#### **Internal Sample Clock**

**Device:** Silicon Labs Si571 Any-Rate VCXO **Type:** Programmable VCXO **Frequency Range:** 10-810 MHz **Start-Up Freq:** 200 MHz **Freq Resolution:** 0.09 ppb **Interface:** FPGA I<sup>2</sup>C Bus 0

#### **Clock Synthesizer**

**Device:** Texas Instruments CDCM7005 Clock Synthesizer **Frequency Dividers:** 1, 2, 4, 6, 8, and 16 **Output Clocks:**Five LVPECL output clocks **Interface:** FPGA

#### Gate

Gate Sources: Selectable from external or internal gate

External: Front panel SSMC TRIG, or Sync Bus LVPECL GATE

Internal: Generated from programmable register

Gate Polarity: Programmable polarity for external gate

Triggering: Gate can be programmed as a trigger with a programmable trigger length

#### Sync

Sync Source: Selectable from external or internal sync External: Front panel SSMC TRIG, or Sync Bus LVPECL SYNC Internal: Generated from programmable register

Sync Pulse Width: 2 clock cycles, minimum

#### **External Trigger Input**

**Connector Type:** Front panel SSMC connector, **TRIG Signal Type:** LVTTL

### Field-Programmable Gate Arrays (FPGA)

Standard: Xilinx Kintex UltraScale XCKU035-2 Option 084: Xilinx Kintex UltraScale XCKU060-2 Option 087: Xilinx Kintex UltraScale XCKU115-2 Configuration: Factory programmed by Pentek: A/D, DDC, IP Cores

#### FPGA MGT Clock Generator

**Device:** Silicon Labs Si5341B Any-Rate Clock Generator **Type:** 10 separate programmable clock outputs **Frequency Range:** 100 Hz to 350 MHz **Interface:** FPGA I<sup>2</sup>C Bus 0

#### RAM memory

Size: 5 Gigabytes of DDR4 SDRAM Speed: 1200 MHz (2400 MHz DDR) Bus Width: 80 bits Interface: FPGA

#### **Configuration FLASH memory**

**Size:** 1 Gigabit **Bus Width:** 16 bits **Interface:** FPGA

#### XMC Interfaces

# PCI Express Interface

XMC Connector: 114-pin (XMC standard Pn5 connector), **P15** Compliance: ANSI/VITA 42.3 XMC PCI Express Protocol Standard Lanes/Speed: Gen1 x8 - 2 GB/sec Gen2 x8 - 4 GB/sec Gen3 x8 - 8 GB/sec **Secondary XMC Interface** (Option 105) XMC Connector: 114-pin (XMC standard Pn6 connector), **P16**

Compliance: ANSI/VITA 42.0 XMC Standard Protocol (user must implement these protocols with user FPGA code): ANSI/VITA 42.2 XMC Serial RapidIO Protocol Standard ANSI/VITA 42.3 XMC PCI Express Protocol Standard ANSI/VITA 42.5 Aurora Pin Assignments

#### **PMC Interface** (Option 104)

**PMC Connector:** 64-pin PMC standard Pn4 connector, **P14 Compliance:** 48 I/O lines routed to the FPGA as 24 LVDS pairs or 48 LVCMOS single-ended (2.5V) **Note:** Not 3.3V tolerant

#### **Temperature and Voltage Sensors**

#### Main PCB Temperature

Quantity: Four temperature sensors Controller: Texas Instruments LM95234 Interface: FPGA I<sup>2</sup>C Bus 0

#### Main PCB Power

Quantity: Four voltage inputs (two for 3.3V, two for 12V) Controller: Linear Technology LTC2990 Interface: FPGA I<sup>2</sup>C Bus 0

#### Main PCB Voltage

Quantity: Ten voltage sensors Controller: Kintex UltraScale System Monitor Interface: FPGA Front Panel Interface Module Temperature

Quantity: Three temperature sensors Controller: Texas Instruments LM83 Interface: FPGA I<sup>2</sup>C Bus 0

#### Nominal Power Consumption\*

| Current Draw:                               | +3.3V (Watts) | VPWR (12V or 5V) (Watts) | Total |  |  |

|---------------------------------------------|---------------|--------------------------|-------|--|--|

| XCKU035 (Standard)                          | TBD           | TBD                      | TBD   |  |  |

| XCKU060 (Option 084)                        | 4.79          | 32.61                    | 37.4  |  |  |

| XCKU115 (Option 087)                        | 2.68          | 37.33                    | 40.02 |  |  |

| *With factory IP at the maximum clock rate. |               |                          |       |  |  |

#### **Physical**

Dimensions: Single PMC/XMC board Depth: 149.0 mm (5.87 in) Height: 74 mm (2.91 in)Weight: Approximately 14 oz (400 grams), with 2-slot heatsink

#### **Environmental**

Standard: Level L0 Cooling Method (operational): Forced Air Operating Temp: 0° to 50° C Storage Temp: –20° to 90° C Relative Humidity: 0 to 95%, non-condensing Pentek Ruggedization Level L1 Pentek Option Number: -701 Cooling Method (operational): Forced Air Operating Temperature: 0° to 50° C Storage Temperature: -40° C to +100° C Sine Vibration: 2g, 20–500 Hz Random Vibration: 0.01g2/Hz, 20-2000 Hz Shock: 10g, 11ms **Relative Humidity:** No conformal coating: 0% to 95% non-condensing Conformal coating (Option 720): 0% to 100% non-condensing Pentek Ruggedization Level L2 Option Number: -702 Cooling Method (operational): Forced Air Operating Temperature: -20° to 65° C Storage Temperature:  $-40^{\circ}$  C to  $+100^{\circ}$  C

Sine Vibration: 2g, 20–500 Hz Random Vibration: 0.04g2/Hz, 20–2000 Hz Shock: 20g, 11ms Relative Humidity: No conformal coating: 0% to 95% non-condensing Conformal coating (Option 720): 0% to 100% non-condensing **Pentek Ruggedization Level L3** Option Number: –713 Cooling Method (operational): Conduction Cooled Operating Temp: –40° to 70° C Storage Temp: –50° to 100° C Relative Humidity: 0 to 95%, non-condensing

# **Chapter 2: Installation and Connections**

# Inspection

After unpacking, inspect the unit carefully for possible damage to connectors or components. If any damage is discovered, contact Pentek immediately at (201) 818–5900. Please save the shipping container and packing material in case reshipment is required.

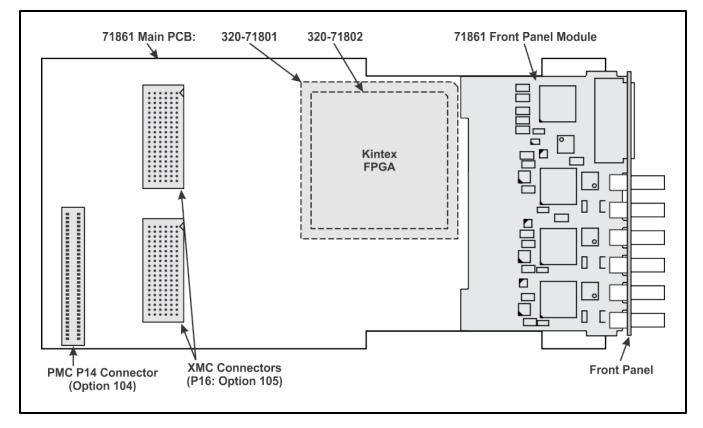

The simplified assembly drawing of Model 71861 (below) shows the complete PCB assembly as shipped, including the front panel I/O module and the connectors for Options 104 and 105. Depending on the FPGA option ordered, there are two different main PCBs, part number 320–71801 or 320–71802 as identified below, to accommodate different Kintex FPGA physical profiles.

Note that a heat sink can be mounted on the Model 71861 PCB assembly as shipped.

Minimum System Requirements: The system in which you install this Pentek product should have the latest Intel® Core<sup>™</sup> i7 processor with a minimum RAM of 8 GB. PCIe Gen 3 x8 is required. Model 71861 is shipped to boot with Gen 3 x8 PCIe default FPGA code. For more information, refer to "DIP Switch Settings" on the next page.

# **DIP Switch Settings**

This section describes operating parameters that are set by DIP switch **SW1** on the Model 71861 main PCB (Pentek part number 320–71801 or 320–71802). As shipped from the factory, all switches are set in default positions on your board. The default operating parameters they select may or may not meet your requirements. Before installing your board, please review the default settings shown in the table below to determine whether you need to change any of these settings.

You should not change any switches that are not described in this section; those are reserved for factory test and setup purposes only.

Use a ballpoint tip only for setting DIP switches. DO NOT USE paper clips, tweezers, or any other sharp objects, as they may damage the switch.

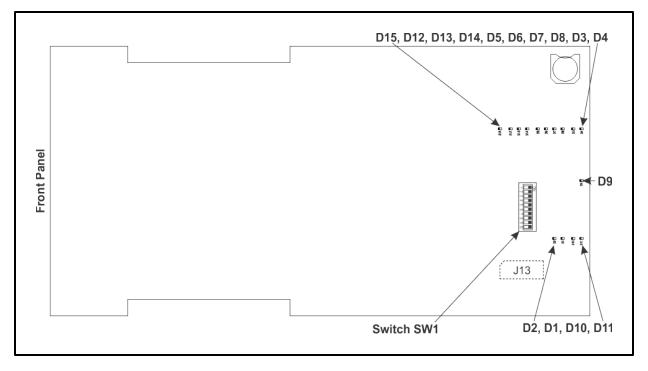

**SW1** is located on the solder side of the main PCB, as shown in the drawing below, and is accessible while the heat sink is mounted on the PCB. (Refer to "PCB LEDs" on page 26 for a description of the LEDs identified below, and "JTAG Connector" on page 29 for a description of the JTAG connector **J13** shown below).

#### Main PCB, Solder Side

Switch **SW1** controls access to the FPGA configuration functions. The table below shows the settings for this switch.

| SW1 – FPGA Configuration                                                                                                |                                                                           |                                 |              |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------|--------------|--|--|--|

| Switch                                                                                                                  | Function ON OFF                                                           |                                 |              |  |  |  |

| SW1-1                                                                                                                   | FLASH Memory Write Protect/Write<br>Enable                                | Write Protected Write Enabled   |              |  |  |  |

| SW1-2                                                                                                                   | FLASH Memory V <sub>PP</sub>                                              | Voltage Applied No Voltage      |              |  |  |  |

| SW1-3                                                                                                                   | Select Root Configuration at power on                                     | Soo tho to                      | blabalow     |  |  |  |

| SW1-4                                                                                                                   | I-4 Select Boot Configuration at power on See the tabl                    |                                 |              |  |  |  |

| SW1-5                                                                                                                   | PCIe Clock Select                                                         | XMC P15 Clock<br>* On-board Clo |              |  |  |  |

| SW1-6                                                                                                                   | P16 Clock Select                                                          | XMC P16 Clock On-board Clo      |              |  |  |  |

| SW1-7                                                                                                                   | JTAG Source Select                                                        | XMC JTAG                        | Board JTAG * |  |  |  |

| SW1-8                                                                                                                   | SW1-8 JTAG Bypass (factory use only) <sup>a</sup> Not Bypassed Bypassed * |                                 |              |  |  |  |

| SW1-9 Not connected -                                                                                                   |                                                                           | -                               |              |  |  |  |

| SW1-10                                                                                                                  | SW1-10         User Spare         -         -                             |                                 |              |  |  |  |

| * Factory default settings<br><b>Note:</b> For Model 78861, JTAG Source Select will be set to ON (XMC JTAG) by default. |                                                                           |                                 |              |  |  |  |

| FPGA Configuration Select – Switches SW1–3:4 |                                          |                                     |  |  |  |

|----------------------------------------------|------------------------------------------|-------------------------------------|--|--|--|

| SW1-3                                        | SW1-3 SW1-4 Configuration Select (FLASH) |                                     |  |  |  |

| ON *                                         | ON *                                     | Version 0 Boot Code - Gen 3 x8 PCIe |  |  |  |

| OFF                                          | ON                                       | Version 1 Boot Code                 |  |  |  |

| ON                                           | OFF                                      | Version 2 Boot Code                 |  |  |  |

| OFF OFF Version 3 Boot Code                  |                                          |                                     |  |  |  |

| * Factory default setting                    |                                          |                                     |  |  |  |

Model 71861 is shipped with a default FPGA configuration on FLASH memory, which is loaded at power–up. Up to four FPGA configurations can be stored in FLASH, identified as Version 0, Version 1, Version 2, and Version 3. The Pentek default FPGA configuration is located in the Version 0 space. The other three positions are empty.

The Pentek default FPGA configuration sets the PCIe interface to Gen 3 x8. However, the board can negotiate down to Gen 2 or Gen 1 x4, as needed.

**aSW1-8** (factory use only) selects whether all JTAG-linked components on the board are inserted into the JTAG chain or whether only the Kintex FPGA is in the JTAG chain. Only the Kintex can be user modified. Customers should maintain the factory setting of "bypassed". When not bypassed, JTAG activity may affect the PCIe link.

# PCB LEDs

The PCB LEDs, labeled **Dnn**, are positioned on the solder side of the 71861 main PCB, as shown below. The use of each LED is indicated in the table below.

| PCB LED Use |                     |                                                                    |                                       |     |     |     |    |

|-------------|---------------------|--------------------------------------------------------------------|---------------------------------------|-----|-----|-----|----|

| LED         | Color               |                                                                    | USE                                   |     |     |     |    |

| D1          | Green               | Power supply sequencer d                                           | one                                   |     |     |     |    |

| D2          | Red                 | Power supply sequencer fa                                          | ault detected                         | d   |     |     |    |

| D3          | Green               | Kintex FPGA initialization of                                      | complete                              |     |     |     |    |

| D4          | Red                 | Kintex FPGA initialization in                                      | n progress                            |     |     |     |    |

| D5          | Green               | Kintex PCIe link has been e                                        | Kintex PCIe link has been established |     |     |     |    |

|             | Kintex active lanes |                                                                    | x1                                    | x2  | x4  | x8  |    |

| D6<br>D7    | Yellow              | (LED0 = D6 and LED1 =                                              | D6                                    | Off | On  | Off | On |

| Di          | D                   | D7):                                                               | D7                                    | Off | Off | On  | On |

| D8          | Green               | Kintex P16 link has been e                                         | stablished                            |     |     |     |    |

| D9          | Green               | User-defined LED                                                   |                                       |     |     |     |    |

| D10         | Red                 | System monitor alarm                                               |                                       |     |     |     |    |

| D11         | Red                 | Temperature alarm                                                  |                                       |     |     |     |    |

| D12         | Green               | CDCM7005 VCXO is OK                                                |                                       |     |     |     |    |

| D13         | Green               | CDCM7005 reference clock is OK                                     |                                       |     |     |     |    |

| D14         | Green               | CDCM7005 is locked                                                 |                                       |     |     |     |    |

| D15         | Red                 | 0.75 V (FPGA Core Power) power failure (LED is off if power is OK) |                                       |     |     |     |    |

## **Baseboard Connectors**

The following sections describe the baseboard PMC/XMC connectors on the 71861 PCB.

### **XMC Connectors**

Model 71861 provides an XMC high-speed serial connector, identified as **P15**, that complies with the VITA 42.3 XMC Switched Mezzanine Card Auxiliary Standard. This interface is configured as PCI Express Gen 3 x8.

Option 105 for the 71861 provides high-speed serial connections from FPGA spare pins using XMC connector **P16**. This connector complies with the VITA 42.0 XMC Standard and can support various interfaces including VITA 42.2 Serial RapidIO, VITA 42.3 PCI Express, or VITA 42.5 Aurora.

| Option 105 XMC P16 FPGA Pin Connections |                                                                                                                                           |                   |     |          |          |     |

|-----------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-----|----------|----------|-----|

| Pin                                     | Α                                                                                                                                         | В                 | С   | D        | Е        | F   |

| 01                                      | S2_TD_P0                                                                                                                                  | S2_TD_N0          | n/c | S2_TD_P1 | S2_TD_N1 | n/c |

| 02                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 03                                      | S2_TD_P2                                                                                                                                  | S2_TD_N2          | n/c | S2_TD_P3 | S2_TD_N3 | n/c |

| 04                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 05                                      | S3_TD_P0                                                                                                                                  | S3_TD_N0          | n/c | S3_TD_P1 | S3_TD_N1 | n/c |

| 06                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 07                                      | S3_TD_P2                                                                                                                                  | S3_TD_N2          | n/c | S3_TD_P3 | S3_TD_N3 | n/c |

| 08                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 09                                      | n/c                                                                                                                                       | n/c               | n/c | n/c      | n/c      | n/c |

| 10                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 11                                      | S2_RD_P0                                                                                                                                  | S2_RD_N0          | n/c | S2_RD_P1 | S2_RD_N1 | n/c |

| 12                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 13                                      | S2_RD_P2                                                                                                                                  | S2_RD_N2          | n/c | S2_RD_P3 | S2_RD_N3 | n/c |

| 14                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 15                                      | S3_RD_P0                                                                                                                                  | S3_RD_N0          | n/c | S3_RD_P1 | S3_RD_N1 | n/c |

| 16                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 17                                      | S3_RD_P2                                                                                                                                  | S3_RD_N2          | n/c | S3_RD_P3 | S3_RD_N3 | n/c |

| 18                                      | GND                                                                                                                                       | GND               | n/c | GND      | GND      | n/c |

| 19                                      | XMC_REFCLK1_<br>P                                                                                                                         | XMC_REFCLK1_<br>N | n/c | n/c      | n/c      | n/c |

|                                         | Sn_TD_Pm, Sn_TD_Nm = Serial Transmit, FPGA Auxiliary Port n, lane m<br>Sn_RD_Pm, Sn_RD_Nm = Serial Receive, FPGA Auxiliary Port n, lane m |                   |     |          |          |     |

The table below identifies the FPGA to XMC **P16** pin connections.

### PMC Connector (Option 104)

Option 104 for Model 71861 provides connections from FPGA spare pins to the baseboard or carrier using PMC connector **P14**. These connections are programmed for low-voltage differential signals (LVDS) in the default FPGA configuration; you can reconfigure these pins with custom FPGA programming (see "Navigator FPGA Design Kit (FDK)" on page 13).

The P14 signals can be configured in the FPGA as either LVDS (the default) or LVCMOS, but in either case are limited to 2.5V, and also cannot be driven with a negative voltage.

The table below identifies the LVDS signals that are connected from the FPGA to the PMC **P14** connector pins.

| Option 104 PMC FPGA Pin Connections |             |               |             |  |  |

|-------------------------------------|-------------|---------------|-------------|--|--|

| FPGA Signal                         | PMC P14 Pin | FPGA Signal   | PMC P14 Pin |  |  |

| P14_DATA_N0                         | 2           | P14_DATA_N16  | 1           |  |  |

| P14_DATA_P0                         | 4           | P14_DATA_P16  | 3           |  |  |

| P14_DATA_N1                         | 6           | P14_DATA_N17  | 5           |  |  |

| P14_DATA_P1                         | 8           | P14_DATA_P17  | 7           |  |  |

| P14_DATA_N2                         | 10          | P14_DATA_N18  | 9           |  |  |

| P14_DATA_P2                         | 12          | P14_DATA_P18  | 11          |  |  |

| P14_DATA_N3                         | 14          | P14_DATA_N19  | 13          |  |  |

| P14_DATA_P3                         | 16          | P14_DATA_P19  | 15          |  |  |

| P14_DATA_N4                         | 18          | P14_DATA_N20  | 17          |  |  |

| P14_DATA_P4                         | 20          | P14_DATA_P20  | 19          |  |  |

| P14_DATA_N5                         | 22          | P14_DATA_N21  | 21          |  |  |

| P14_DATA_P5                         | 24          | P14_DATA_P21  | 23          |  |  |

| P14_DATA_N6                         | 26          | P14_DATA_N22  | 25          |  |  |

| P14_DATA_P6                         | 28          | P14_DATA_P22  | 27          |  |  |

| P14_DATA_N7                         | 30          | P14_DATA_N23  | 29          |  |  |

| P14_DATA_P7                         | 32          | P14_DATA_P23  | 31          |  |  |

| P14_DATA_N8                         | 34          | not connected | 33          |  |  |

| P14_DATA_P8                         | 36          | not connected | 35          |  |  |

| P14_DATA_N9                         | 38          | not connected | 37          |  |  |

| P14_DATA_P9                         | 40          | not connected | 39          |  |  |

| P14_DATA_N10                        | 42          | not connected | 41          |  |  |

| Option 104 PMC FPGA Pin Connections |             |               |             |  |  |  |  |

|-------------------------------------|-------------|---------------|-------------|--|--|--|--|

| FPGA Signal                         | PMC P14 Pin | FPGA Signal   | PMC P14 Pin |  |  |  |  |

| P14_DATA_P10                        | 44          | not connected | 43          |  |  |  |  |

| P14_DATA_N11                        | 46          | not connected | 45          |  |  |  |  |

| P14_DATA_P11                        | 48          | not connected | 47          |  |  |  |  |

| P14_DATA_N12                        | 50          | not connected | 49          |  |  |  |  |

| P14_DATA_P12                        | 52          | not connected | 51          |  |  |  |  |

| P14_DATA_N13                        | 54          | not connected | 53          |  |  |  |  |

| P14_DATA_P13                        | 56          | not connected | 55          |  |  |  |  |

| P14_DATA_N14                        | 58          | not connected | 57          |  |  |  |  |

| P14_DATA_P14                        | 60          | not connected | 59          |  |  |  |  |

| P14_DATA_N15                        | 62          | not connected | 61          |  |  |  |  |

| P14_DATA_P15                        | 64          | not connected | 63          |  |  |  |  |

### JTAG Connector

The Model 71861 PCB **J13** JTAG connector provides an interface to download programs and to perform boundary-scan tests on 71861 devices. This connector is located on the solder side of the Model 71861 main PCB (Pentek part number 320–71801 or 320–71802), as illustrated in "Main PCB, Solder Side" on page 24.

The table below gives the pinout for this 10-pin header.

| Pentek JTAG J13 Connector |            |                             |            |        |  |  |  |

|---------------------------|------------|-----------------------------|------------|--------|--|--|--|

| Signal                    | Pin Number |                             | Pin Number | Signal |  |  |  |

| GND                       | 1          | 1 2                         | 2          | +3.3 V |  |  |  |

| GND                       | 3          | 3 ■ ■ 4<br>5   ■ ■   6      | 4          | TMS    |  |  |  |

| GND                       | 5          | 7 ¦ ■ ■ ¦ 8<br>9 ' ■ ■ ! 10 | 6          | тск    |  |  |  |

| GND                       | 7          |                             | 8          | TDO    |  |  |  |

| GND                       | 9          | ]                           | 10         | TDI    |  |  |  |

# **Battery Installation**

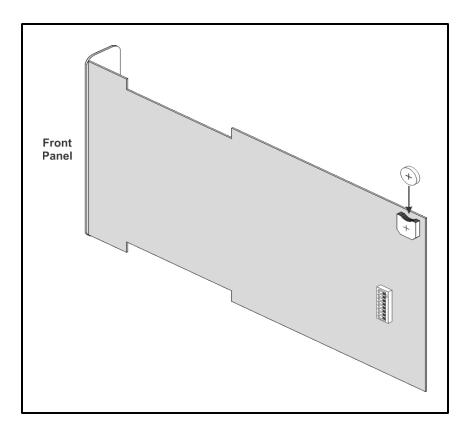

Your Model 71861 shipment includes a battery in a separate package, identified as part number 174.50010. If you plan to use the Kintex FPGA bitstream encryption capability, such as with Pentek's Navigator FDK, the battery must be installed on the solder side of the main PCB (part number 320–71801 or 320–71802) as shown in the drawing below. Ensure that the battery positive terminal is facing the outside of the battery holder.

### Perform all assembly steps at an antistatic workstation.

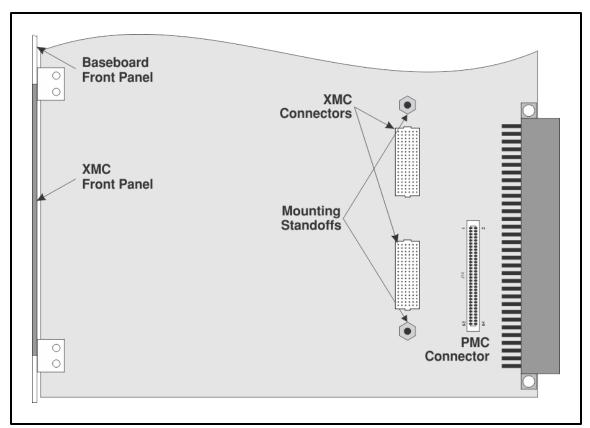

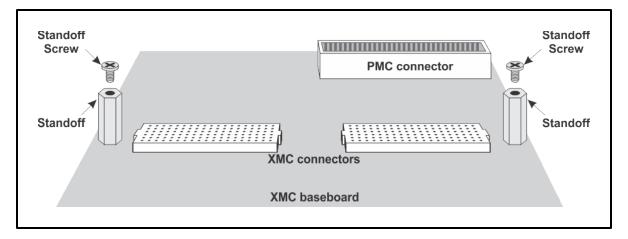

Model 52861 (Model 71861 on a Pentek Model 5201 3U VPX carrier) and Model 53861 (Model 71861 on a Pentek Model 5306 3U VPX carrier) are shipped with the battery already installed because the battery cannot be installed without removing the Model 71861 XMC from the VPX carrier. Model 71861 mounts on the connector side of an XMC baseboard or carrier. Refer to the operating manual supplied with your baseboard for any specific mounting instructions. A typical XMC baseboard is shown below.

**Minimum System Requirements:** The system in which you install this Pentek product should have the latest Intel® Core<sup>TM</sup> i7 processor with a minimum RAM of 8 GB. PCIe Gen 3 x8 is required.

**REMOVE POWER to the XMC baseboard before installation!**

The Model 71861 requires both a 3.3V and a 5V or 12V power supply (12V is recommended). Ensure that the XMC baseboard or carrier you are using has both a 3.3V and a 5V or 12V power supply.

## Typical XMC Baseboard

### **Installation Instructions**

- 1. Attach an ESD strap to your wrist—attach the other end to a ground source. The ESD strap must be secured both to your wrist and to ground throughout the procedure.

- 2. Pentek XMC baseboards are supplied with module standoffs and mounting screws installed. Ensure that the standoffs on your baseboard are installed at the locations shown in the drawing below and in the Typical XMC Baseboard drawing above.

- 3. Remove the blank module front panel from the front panel of the XMC baseboard (see the Typical XMC Baseboard drawing, above).

- 4. Position the Model 71861 front panel into the opening from behind the baseboard front panel, and position the module so that the 71861 XMC connectors are over the XMC connectors on the baseboard (see the Baseboard PMC/XMC Connections drawing, below).

### **Baseboard PMC/XMC Connections**

- 5. **GENTLY but firmly**, press down on the 71861 board opposite the connectors to fully seat the board's connectors into the baseboard. The connectors on the underside of the 71861 PCB should connect smoothly with the corresponding connectors on the baseboard.

- 6. Using two flat-head Phillips standoff screws (supplied with the 71861), secure the Model 71861 PCB, through the PCB's standoff holes, to the baseboard's standoffs (see the Baseboard PMC/XMC Connections drawing, above).

# **Front Panel Connections**

The Model 71861 XMC front panel, shown in the drawing on the left, includes six SSMC coaxial connectors for clock, trigger, and analog input signals, and a 26- pin Sync Bus input/output connector. These connectors are described below.

The front panel also includes ten LED indicators, which are described in "Front Panel LEDs" on page 36.

# **Clock Input Connector**

The front panel has one SSMC coaxial connector, labeled **CLK**, for input of an external sample clock. The external clock signal must be a sine wave or square wave of +0 dBm to +10 dBm, with a frequency range from 10 to 800 MHz.

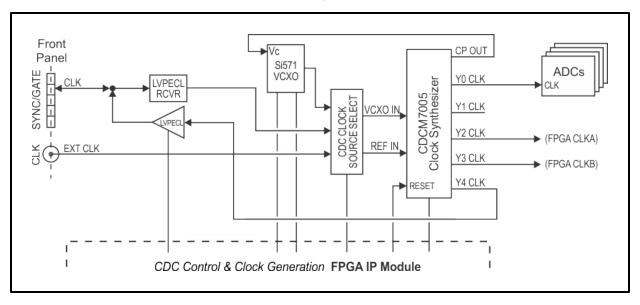

This external clock input can be used as the sample clock signal for the A/D converters. The program-selected clock source is input to a CDCM7005 Clock Synthesizer that generates five separate output clocks, each programmable as sub-multiples of the input frequency. One of the CDCM7005 output clocks (Y0) provides the sample clock for the ADS5485 A/D converters.

When greater than 200 MHz, the input clock must be divided down by the CDCM7005 for the ADC sample clock.

Take care that the ADC clock output from the CDCM7005 never exceeds the ADS5485's rated clock speed during any change of frequency with the VCXO and/or the CDCM7005.

- If you are increasing the VCXO frequency, first adjust the appropriate CDC divider so that the ADS5485 clock does not exceed 200 MHz.

- If you are decreasing the VCXO frequency, do not adjust the CDC divider until the VCXO has been reprogrammed so that the ADS5485 clock does not exceed 200 MHz.

# **Trigger Input Connector**

The front panel has one SSMC coaxial connector, labeled **TRIG**, for input of an external trigger. The external trigger signal must be an LVTTL signal.

The front panel **TRIG** input is 5V tolerant but it must NOT have any negative voltage applied. It is terminated with a 392–ohm resistor to 3.3V and a 332–ohm resistor to ground.

The trigger input can be used as a gate or trigger for A/D signal processing.

### **Analog Signal Input Connectors**

The front panel has four SSMC coaxial connectors for analog signal inputs, labeled **IN 1**, **IN 2**, **IN 3**, and **IN 4**, one for each ADS5485 A/D converter.

Each analog input signal has a full-scale level of +8 dBm. Each input drives an RF transformer with 50-ohm input impedance.

### Sync Bus Connector

The 26-pin Sync Bus front panel connector, labeled **SYNC/GATE**, provides clock, sync, and gate input/output pins for the Low-Voltage Positive Emitter-Coupled Logic (LVPECL) Sync Bus. When Model 71861 is a bus Master, these pins output LVPECL Sync Bus signals to other slave units. When Model 71861 is a bus Slave, these pins input LVPECL signals from a bus Master. This connector also accepts two Low-Voltage TTL (LVTTL) Gate/Sync inputs.

The table below shows the **SYNC/GATE** connector pin configuration. The mating 26–pin connector is Pentek part # 353.02607 (Model 2140–998).

| SYNC/GATE Connector Pins |     |            |     |          |     |                 |  |  |

|--------------------------|-----|------------|-----|----------|-----|-----------------|--|--|

| Signal                   | Pin |            |     |          | Pin | Signal          |  |  |

| LVTTL<br>GATE/TRIG       | B1  |            |     | 1        | A1  | GND             |  |  |

| LVTTL SYNC/PPS           | B2  | B1 ►<br>B2 | ••  | A1<br>A2 | A2  | GND             |  |  |

| LVPECL GATE-             | B3  | B2<br>B3   |     | A2<br>A3 | A3  | LVPECL GATE+    |  |  |

| GND                      | B4  | B4         | • • | A4       | A4  | GND             |  |  |

| LVPECL SYNC-             | B5  | B5<br>B6   | ••  | A5<br>A6 | A5  | LVPECL<br>SYNC+ |  |  |

| GND                      | B6  | B7         | • • | A7       | A6  | GND             |  |  |

| LVPECL CLK-              | B7  | B8<br>B9   |     | A8<br>A9 | A7  | LVPECL CLK+     |  |  |

| GND                      | B8  | B10        | • • | A10      | A8  | GND             |  |  |

| Spare                    | B9  | B11        | • • | A11      | A9  | Spare           |  |  |

| GND                      | B10 | B12<br>B13 |     | A12      | A10 | GND             |  |  |

| Spare                    | B11 | 613        | ••• | A13      | A11 | Spare           |  |  |

| GND                      | B12 |            |     |          | A12 | GND             |  |  |

| Spare                    | B13 |            |     |          | A13 | Spare           |  |  |

When connecting LVPECL Sync Bus pins to additional Model 71861 modules, the LVPECL pins on the LAST unit must be terminated. Pentek includes a terminating board (part # 004.71504, Model # 2140–999) with your shipment for this purpose.

The LVTTL GATE/TRIG and SYNC/PPS signals are 5V tolerant but they must NOT have any negative voltage applied. They are terminated with a 392-ohm resistor to 3.3V and a 332-ohm resistor to ground.

## Front Panel LEDs

The Model 71861 XMC front panel has ten LED indicators, as shown in the drawing in "Front Panel Connections" on page 33.

### Link LED

The green **LNK** LED indicates the link speed when a valid link has been established over the PCIe interface, as follows:

- Gen 1 LNK LED will blink slowly (less than once per second)

- Gen 2 LNK LED will blink approximate once per second

- Gen 3 LNK LED will be constantly on

### User LED

The green **USR** LED is for user applications.

### Master LED

The yellow **MAS** LED illuminates when this 71861 is the Sync Bus Master. When only a single 71861 is used, it must be a Master.

### PPS LED

The green **PPS** LED illuminates when a valid PPS signal is detected. The LED will blink at the rate of the PPS signal.

### **Over Temperature LED**

The red **TMP** LED illuminates when an over-temperature or over-voltage condition is indicated by any of the temperature/voltage sensors on the 71861 PCB.

### Clock LED

The green **CLK** LED illuminates when a valid sample clock signal is detected. If the LED is not illuminated, no clock has been detected and no data from the input stream can be processed.

### ADC Overload LEDs

There are four red **OV** LEDs, one for each A/D input. Each LED indicates either an overload detection in the associated ADS5485, or an ADC FIFO overrun.

# **Chapter 3: Hardware Resource Operation**

# Overview

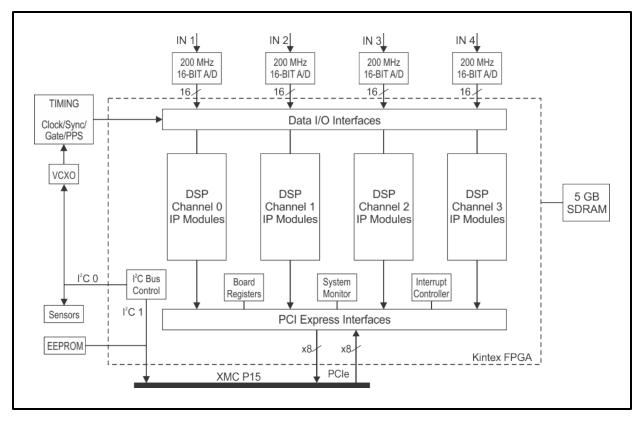

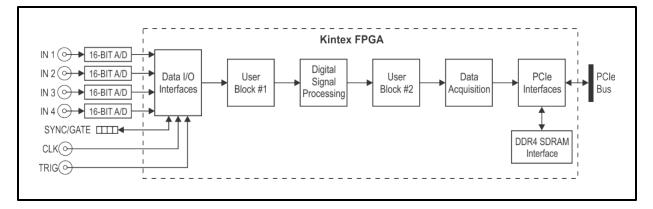

This chapter describes operation of the Model 71861 hardware resources. The block diagram below shows the overall data flow of the 71861.

The functional blocks in the diagram are described in the sections that follow.

- "Analog to Digital Input" on the next page

- "Timing and Synchronization" on page 39

- "Interrupt Operation" on page 41

- "FPGA System Monitor" on page 42

- "I2C Bus Controllers" on page 43

- "RAM Memory Operation" on page 50

- "FLASH Memory Operation" on page 50

Refer to "FPGA IP Core Operation" on page 51 for a description of the FPGA IP Core modules data processing.

# Analog to Digital Input

Model 71861 accepts four analog RF inputs on front panel SSMC connectors, labeled **IN 1**, **2**, **3**, and **4** (see "Front Panel Connections" on page 33). Each input is transformer coupled, digitized by a Texas Instruments ADS5485 200–MHz, 16–bit A/D converter (ADC), and then routed to the FPGA for processing by the IP Core modules.

The processed data can be read through the PCIe interface using input DMA engines.

The simplified block diagram below shows the analog to digital input data flow.

Refer to "FPGA IP Core Operation" on page 51 for a description of each of the top-level functional blocks of the FPGA IP code.

Refer to the TI ADS5485 datasheet (see "Supporting Documentation" on page 17) for a description of ADS5485 operation.

# Timing and Synchronization

The Model 71861 front panel Sync Bus Connector provides clock, sync, PPS, and gate input/output signals. The front panel also has two coaxial SSMC connectors for input of an external sample clock and an external gate/trigger.

The front panel interface allows one Model 71861 to act as a Master, driving the clock, sync, and/or gate signals to the Sync Bus. Up to three Slave 71861s can be driven by the Sync Bus, supporting synchronous sampling and sync functions across all connected boards. If more than four boards need to be synchronized, Pentek's Model 7893 Clock Generator allows synchronization of up to eight boards. Note that the Model 7893 is a PCIe board.

#### Clocks

Model 71861 clocks can be selected from the front panel Sync Bus LVPECL CLK input (see "Front Panel Connections" on page 33), the front panel SSMC CLK input (see "Clock Input Connector" on page 33), or the onboard Si571 VCXO. The selected clock source is input to a CDCM7005 Clock Synthesizer that generates five output clocks, each independently programmable. CDCM7005 clock Y0 provides the sample clock for the four ADS5485 ADCs, and clock Y2 provides FPGA CLK for ADC data processing in the FPGA.

When the Model 71861 is a Clock Master, CDCM7005 clock Y4 is output to the CLK pins of the Sync Bus (see "Front Panel Connections" on page 33).

The drawing below illustrates the clock logic. Use the CDCM7005 Control & Clock Generation FPGA IP Core modules to control these clock signals.

## Sync Bus

Model 71861 provides SYNC, GATE, and PPS signals for ADC and user applications. These signals can be driven from the front panel Sync Bus connector LVPECL or TTL inputs (see "Front Panel Connections" on page 33), the front panel TRIG SSMC connector input (see "Trigger Input Connector" on page 33), or a Gate/Sync/PPS Generate Register write.

When Model 71861 is a Sync/Gate Master, a Generate Register write, Sync Bus TTL input, or TRIG input signal is output to the Sync Bus LVPECL SYNC or GATE pins.

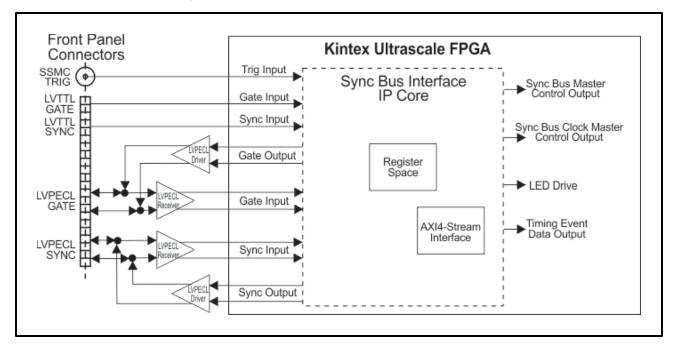

The diagram below illustrates the sync bus logic. Use the Sync Bus Interface FPGA IP Core module to control these signals.

# **Interrupt Operation**

The Model 71861 XMC can generate INTA interrupts in legacy mode or MSI interrupts. Refer to the Operating Manual supplied with your XMC baseboard for a description of the board's interrupt response operation.

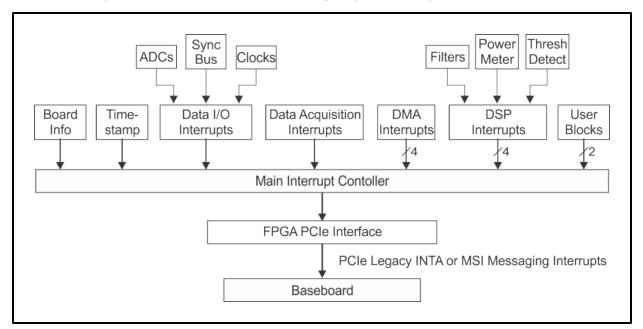

The block diagram below illustrates the interrupt signal routing on Model 71861.

Interrupt events are edge-detected and latched in second-level interrupt flag registers. In addition, the interrupt sources are also routed to dynamic interrupt status registers. The interrupt edges from various sources can be individually enabled by interrupt enable registers and then OR'ed per system module to form sources to the first-level interrupt flag register where the event is latched. Enable bits in the first-level interrupt enable register can individually enable each module's flag, which are then OR'ed together for a single level interrupt input to the PCIe interface.

Clearing an interrupt in the first-level interrupt flag register will turn off the interrupt. The sources are still latched in the second-level flag register but a new interrupt will not be asserted even if the source is still present until the second-level flag is cleared and the logic subsequently detects a new edge.

Use the Interrupt Controller FPGA IP Core module to control the FPGA PCIe interface interrupt signals.

## FPGA System Monitor

The Kintex FPGA System Monitor measures several board power supplies and FPGA on-chip voltages. The "System Monitor Measurement Ports" below table below lists the parameters measured by the System Monitor measurement ports and the required multiplication factors to apply to the readings (System Monitor ports VAUX5 to VAUX7 are not used in the Model 71861).

| System Monitor Measurement Ports |                                             |                                       |  |  |

|----------------------------------|---------------------------------------------|---------------------------------------|--|--|

| Port                             | Port Parameter Measured Measurement Scaling |                                       |  |  |

| VAUX0                            | VPWR (5 or 12V)                             | Voltage = VoltageReading x 14         |  |  |